|

||||

|

|

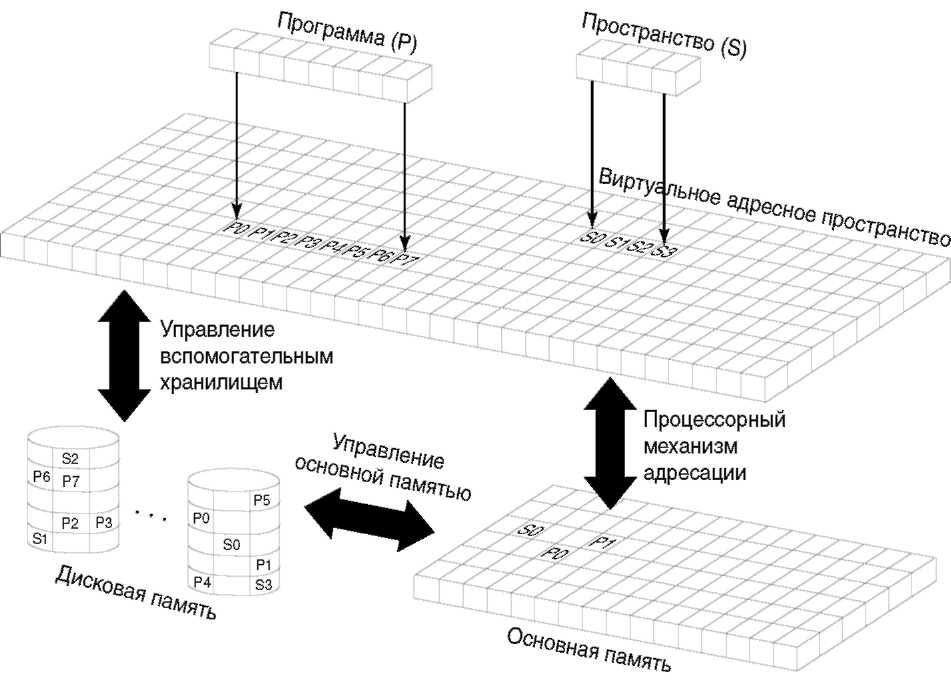

Глава 8 Одноуровневая память Сегодня в компьютерной индустрии модны длинные адреса (в данном случае, «длинный» означает больше 32 разрядов). Практически все производители аппаратуры и ОС начали использовать их в своих продуктах, а в качестве стандарта для следующего поколения предусматривают 64 разряда. Переход на адреса большего размера стимулируется новыми приложениями, такими как хранилища данных, а также снижением цен на основную память. Заказчики отмечают значительное повышение производительности при использовании памяти большого размера, и размеры памяти, измеряемые гигабайтами, становятся обычным делом. 32-разрядный адрес, способный поддерживать размеры памяти только до 4 ГБ, быстро устаревает. Довольно долго процессоры AS/400 и их предшественники — процессоры System/38 — использовали 48-разрядные адреса. С переходом на RISC-процессоры размер адреса возрос до 64 разрядов. Одноуровневая память с большими адресами — вероятно, один из самых известных компонентов AS/400, и редко какая презентация обходится без упоминания о ней. Это даже странно — ведь одноуровневая память не видима никому и ничему выше уровня MI: ни OS/400, ни прикладным программам, ни даже компиляторам. Она доступна только SLIC, а MI работает с объектами, используя для ссылок на них имена. Пространство — эквивалент памяти на уровне MI, но пространство не очень напоминает одноуровневую память. Программы, и прикладные, и системные адресуют объекты при помощи 16-байтовых указателей; которые точнее было бы называть 128-разрядными (их используют все прикладные программы с момента появления System/38 в 1978 году). Но не все разряды: этого указателя используются, поэтому AS/400 обычно не называют 128-разрядным компьютером. Указатель содержит 64-разрядный адрес одноуровневой памяти, а также несколько разрядов дескриптора и неиспользуемые разряды, зарезервированные для будущих расширений. Возможно, нам следует называть AS/400 128-разрядной системой — согласитесь, это было бы неплохой рекламой. Ведь называет же Digital свой процессор Alpha 64-разрядным, хотя он реализует лишь 41-разрядные адреса! HP также не использует для адреса все 64 разряда в своем процессоре PA RISC 2.0. И все же, я полагаю, мы лучше будем пока говорить о 64 разрядах — по крайней мере, до тех пор, пока до уровня IBM не подтянутся остальные. Кроме того, 64 разряда уже и так дают очень большое адресное пространство. «Но насколько большое?» — спросите Вы. Сколько байтов адресуют 64 разряда Ответ: 16 экзабайтов, что равно примерно 18,4 квинтиллионам байтов (или точнее 18 446 744 073 709 551 616 байтов). Большинство людей не в состоянии представить себе такое число. Как я уже упоминал, число байтов, которые могут быть адресованы с помощью 48 разрядов, примерно равно числу миллиметров расстояния от Земли до Солнца и обратно. Но для 64 разрядов нужна новая аналогия. Ричард Рубин, чьи замечания чрезвычайно помогли в работе над этой книгой, напомнил мне историю, рассказанную Джорджем Гамовым (George Gamow) в книге «One, Two, Three, Infinity». Однажды индийский шах Ширхам пожелал вознаградить своего великого визиря Сисса Бен Дахира за изобретение шахмат. Визирь попросил шаха положить на первую клетку шахматной доски одно зерно пшеницы, на вторую — два, на третью — четыре, на четвертую — восемь и так далее, удваивая число на каждой клетке, пока все 64 клетки не будут заполнены. Общее число зерен должно было бы составить 264 — 1. Гамов подсчитал, что если бушель[ 61 ] пшеницы содержит 5 миллионов зерен, то для покрытия всей доски потребовалось бы 4 триллиона бушелей. Когда Гамов писал свою книгу в 1946 году, мировое производство пшеницы составляло 2 миллиарда бушелей в год. При сохранении производства на том же уровне, всему миру потребовалось бы две тысячи лет, чтобы вырастить требуемое количество зерен. Для тех, кто предпочитает аналогию с миллиметрами, 18 квинтиллионов — это примерно вдвое больше числа миллиметров в световом годе, и всего лишь немногим меньше половины расстояния до Альфы Центавра (ближайшей к Солнечной системе звезде). Ясно, что если мы начнем измерять астрономические расстояния в миллиметрах, то нам потребуется более 64 разрядов. А 128-разрядный указатель дает нам... Так что какие бы аналогии мы не проводили, и как бы себе все это не представляли, 64-разрядная адресация предоставляет огромные возможности. Виртуальная память Одноуровневая память AS/400 получила свое имя в честь первопроходцев разработки виртуальной памяти в 60-х годах. Чтобы понять происхождение этого термина, необходимо углубиться в историю. Впервые виртуальная память появилась в компьютере Atlas, созданном в 1961 в английском городе Манчестере (Manchester). В те годы для изготовления памяти использовалась очень дорогостоящая технология магнитных сердечников. Большим программам требовалось много памяти, зачастую больше, чем было на компьютере. Чтобы программа могла поместиться в памяти, приходилось разбивать ее на малые фрагменты и хранить на магнитных дисках или барабанах. Магнитные барабаны были популярны в начале 60-х годов. Барабан похож на жесткий диск, но у него по одной головке чтения/записи на каждую дорожку. В то время барабаны обеспечивали более высокую производительность по сравнению с дисками, так как исключалось время позиционирования головки на дорожку. С сокращением времени позиционирования барабаны вышли из употребления. При разбиении больших программ на малые фрагменты управление памятью требовало от программиста больших усилий. Если фрагмент программы, который должен был исполняться, находился вне памяти, то программист вставлял команды считывания этого фрагмента в память с диска или барабана. Фрагменты программы назывались оверлеями (overlays), и значительная часть программирования заключалась в создании и управлении ими. Виртуальная память смогла устранить эту проблему. Память увеличилась, и программисты могли больше не беспокоиться о том, поместится ли в нее программа. Управление перемещением данных и программ в большой виртуальной памяти взяла на себя ОС. В 1962 году Т. Д. Килбурн (T.D. Kilburn) с соавторами написал свою статью, посвященную системе памяти компьютера Atlas. В статье были такие слова: «. Система представляет программисту комбинацию память-барабан в виде одноуровневой памяти. Необходимое перемещение данных выполняется автоматически»[ 62 ]. Виртуальная память для систем разделения времени В связи с появлением в конце 60-х годов систем разделения времени — раннего этапа эволюции мультипрограммных ОС — многие производители компьютеров приняли виртуальную память на вооружение. При мультипрограммировании системная память разделена на несколько порций, в каждой из которых находится некоторая программа. Пока одна из программ ожидает завершения операции ввода-вывода, другая может использовать процессор. Если в памяти находится достаточное количество программ, то можно обеспечить постоянную загруженность процессора. Мультипрограммные ОС занимались тогда преимущественно пакетной обработкой. Разделение времени — это разновидность мультипрограммирования, когда у каждого пользователя есть подключенный к компьютеру терминал. Так как при этом пользователи интерактивны (то есть программа управляется командами пользователя за терминалом), то на «раздумья» пользователей уходит какое-то время. Соответственно снижается загрузка процессора. Компьютер такого типа поддерживает больше пользователей, так что в памяти одновременно находится довольно много фрагментов программ. Интерактивным пользователям требуется быстрое время отклика, так что эффективное управление множеством фрагментов программ критически важно. Именно его и должна была обеспечить виртуальная память. В основе систем разделения времени лежала возможность аренды времени центрального компьютера отдельными пользователями из разных организаций. Такой подход был популярен, так как большинство малых фирм не могли позволить себе собственный компьютер. Разделение времени предоставляло им ресурсы большого компьютера за часть цены. Так как пользователи компьютера представляли разные организации, совместное использование информации ими не требовалось. Поддерживая разделение времени, системы виртуальной памяти предоставляли каждому пользователю отдельное адресное пространство. Адресные пространства разных пользователей были изолированы друг от друга, что в определенной степени обеспечивало защиту. При переключении ресурсов компьютера на выполнение программы другого пользователя использовалось новое адресное пространство. Такая операция называлась переключением процессов, где процесс рассматривался как единица работы в системе, выполняемая для пользователя. В прошлом переключение процессов было связано с большими накладными расходами. Нужно было изменить таблицы памяти, очистить регистры и загрузить новые данные. Выполнение всех этих действий требовало большого числа команд процессора, и явно чрезмерных затрат времени. Тогда, в конце 60-х, многие искали способы упростить эту операцию и повысить ее эффективность[ 63 ]. К сожалению, разработчики систем разделения времени решили вынести файловую систему за пределы виртуальной памяти. Они создали два места хранения данных и программ: виртуальную память и файловую систему. В подобной архитектуре данные и программы могут использоваться или изменяться, только если находятся в виртуальной памяти. То есть, прежде чем что-либо сделать, данные и программы нужно переместить в виртуальную память. Менеджер файлов обычной системы поддерживает каталог, связывающий имена файлов с местоположением на диске данных, которые в них содержатся. Менеджер файлов предоставляет некий интерфейс, позволяющий программе открыть файл. Затем данные копируются в буферы памяти, обычно являющиеся частью виртуальной памяти. После этого данные могут использоваться и обрабатываться. Когда программа завершает работу с данными, выполняется операция закрытия, переносящая данные из виртуальной памяти обратно в файловую систему. Простой и знакомый большинству из нас пример подобного механизма — использование текстового процессора на ПК. Сначала пользователь открывает файл, содержащий нужный документ, а затем наблюдает мигание индикатора жесткого диска, пока документ считывается в память. На самом деле, документ сначала переносится в виртуальную память, а затем частично — в реальную память. Когда-то раньше, при конфигурировании ОС нашего ПК, мы определяли размер места на жестком диске, зарезервированный для виртуальной памяти. В мире ПК это пространство иногда называется файлом подкачки. Прокручивая текст на экране, пользователь снова видит, как мигает индикатор жесткого диска. По мере необходимости, новые фрагменты документа считываются в память из зарезервированного пространства на диске. Операция открытия файла создает копию документа. Оригинал же по-прежнему находится на жестком диске в неизменном виде. Копия располагается в дисковом пространстве, зарезервированном под виртуальную память. Менеджер виртуальной памяти и ОС автоматически переносят фрагменты документа по мере необходимости из зарезервированной дисковой области в память, а когда надобность в них отпадает — возвращают обратно. Фактически, если учесть копию в памяти, некоторые фрагменты документа существуют в трех копиях. Когда пользователь заканчивает редактирование и сохраняет документ, текстовый процессор запрашивает, сохранить ли изменения. Другими словами, нужно ли записать обновленную в виртуальной памяти копию обратно в файл на диске для постоянного хранения. Если ответ утвердительный, то копия из виртуальной памяти замещает копию на диске. Одноуровневая виртуальная память В только что описанной реализации виртуальной памяти программист имеет дело с двумя уровнями хранилища: файловая система и виртуальная память разделены. Двухуровневая система хранения вызывает дополнительные накладные расходы. Открытие файла связано с записью на диск в файлы подкачки, а закрытие — требует записи обратно на место постоянного хранения. Сам собой напрашивается альтернативный вариант — работать только с одной копией файла. Ведь если нет двух отдельных копий, то не нужно резервировать пространство на диске для файла подкачки. При таком подходе вся файловая система становится частью виртуальной памяти. Менеджер файлов по-прежнему ведет справочник, но теперь он связывает имя файла с местом в памяти, где находятся данные файла. При открытии и закрытии файла не требуется копировать весь файл из его постоянной области хранения на диске. В буфер памяти копируется только та порция (или запись) с которой пользователь в данный момент работает. Часто говорят и так: файлы всегда используются там же, где хранятся. Все это позволяет повысить общую производительность системы. Одноуровневая память — это именно то, что ставили своей целью создатели первой виртуальной памяти, и именно эта модель была реализована в System/38. В честь первооткрывателей мы решили назвать нашу виртуальную память одноуровневой памятью. И двухуровневая виртуальная память, и одноуровневая используются как буфер. Процессоры могут работать только с данными в памяти, но не на диске. Отличие одноуровневой схемы в том, что память в ней — кэш для всего дискового пространства, а не только для зарезервированной области диска. Кроме того, после изменения файла одним пользователем, это изменение немедленно становится видимым всем остальным, работающим с тем же файлом. Недостаток одноуровневой памяти — большой размер адреса. Адрес должен быть достаточно велик, чтобы покрывать все подключенное к системе дисковое пространство. Возьмем 32-разрядный адрес, используемый во многих современных системах. С его помощью можно адресовать до 4 ГБ, что совершенно недостаточно для адресации всего дискового пространства даже на большом ПК. Таким образом, обычные системы просто вынуждены копировать дисковые данные в свои относительно небольшие виртуальные памяти и обратно. Чтобы устранить это ограничение, в System/38 и первые модели AS/400 был включен 48-разрядный адрес. Теперь AS/400 использует 64-разрядный адрес и для будущих расширений предусмотрены дополнительные разряды адреса. Хоть все это и связано с аппаратными затратами, последние вполне компенсируются возможностями по совместному использованию данных и ростом производительности. Постоянная виртуальная память Размер адреса AS/400 значительно превышает необходимый для покрытия всего дискового пространства. Причина такого положения — другая характеристика одноуровневой памяти, называемая постоянством (persistence). Мы уже говорили об этом в главе 5, посвященной объектам. Объект, обладающий постоянством, остается в памяти системы вечно, даже после своего разрушения, и виртуальное адресное пространство такого постоянного объекта никогда не используется повторно. При разрушении постоянного объекта освобождается все занятое им дисковое пространство, за исключением заголовков. Освобожденное дисковое пространство затем используется для других объектов. То, что виртуальное адресное пространство повторно не используется, устраняет многие проблемы защиты и целостности. Если постоянный объект разрушен и его адресное пространство использовано повторно другим объектом, то любой, у кого был разрешенный указатель на старый объект, сможет адресовать новый объект. Так как указатели могут храниться в памяти где угодно, то большинство схем «сборки мусора» для поиска указателей уничтоженных объектов слишком сложны. В AS/400 же применяется достаточно большой адрес и адресное пространство постоянных объектов повторно не используется. Так что «сборка мусора» в этой системе не нужна. Большинство обычных систем виртуальной памяти борются со «сборкой мусора» другим способом. В ранних схемах виртуальной памяти (по-прежнему используемых некоторыми ОС ПК), каждому пользователю выделяется отдельное виртуальное адресное пространство. Когда пользовательский процесс прекращает свое существование, то же происходит и с его виртуальной памятью. Сохранить адрес где-либо в системе нельзя. Единственное место разделения данных — файловая система, где виртуальная адресация не используется. Для большинства многопользовательских ОС, таких как Unix, подобная реализация неприемлема. Вместо того, чтобы предоставить пользовательской программе возможность прямой адресации виртуальной памяти, такие системы передают программе адрес, который перед использованием транслируется в виртуальный аппаратно. В архитектуре PowerPC такой адрес называется эффективным. Как мы увидим далее, эффективный адрес позволяет добиться некоторого уровня разделения памяти, но за счет больших накладных расходов. Виртуальная память в таких системах логически подразделяется на сегменты — блоки последовательных байтов памяти. Эффективный адрес задает один из таких сегментов. Обычно трансляция эффективного адреса в виртуальный использует несколько (от 4 до 16) регистров микросхемы процессора, которые называются сегментными регистрами. Каждый сегментный регистр содержит виртуальный адрес одного из сегментов памяти. Часть старших разрядов эффективного адреса задают один из сегментных регистров. Остальные же задают байт внутри сегмента (и называются смещением в сегменте). Так как эффективный адрес содержит смещение внутри сегмента виртуального адреса, то данный тип адресации иногда называется адресацией относительно сегмента. Проще всего представить себе эффективный адрес как подмножество виртуального адреса большего размера. Пользовательская программа может напрямую адресовать лишь несколько сегментов виртуальной памяти — те, чьи адреса загружены в сегментные регистры. Программа может запросить у ОС перезагрузку системных регистров, что позволит ей получить доступ к другим сегментам, но по-прежнему будет работать лишь с небольшой частью виртуальной памяти. Например, на некоторых процессорах Intel — лишь четыре сегментных регистра, что позволяет работать только с четырьмя сегментами одновременно, тогда как некоторые ранние процессоры RS/6000 использовали 16 таких регистров, но все равно могли адресовать лишь небольшую часть общей памяти. В архитектуре PowerPC мы избавились от сегментных регистров и заменили их специальной таблицей в памяти, так называемой таблицей сегментов. Это дает пользовательским программам доступ к гораздо большему числу сегментов, чем регистровая реализация. Каждая запись таблицы сегментов по-прежнему содержит виртуальный адрес одного из сегментов виртуальной памяти. Эффективный адрес, используемый программой, теперь задает запись таблицы сегментов и байтовое смещение в сегменте. Две программы могут использовать совместно один и тот же виртуальный адрес, если они обращаются к одной и той же записи в таблице сегментов, или если тот же самый виртуальный адрес хранится в нескольких записях таблицы. В случае адресации относительно сегмента, пользовательской программе виден только эффективный адрес, и таким образом, она не может сохранить где-либо виртуальный адрес. Трансляция эффективного адреса в виртуальный требует дополнительных накладных расходов, но зато виртуальные адреса защищены и не нужна «сборка мусора». Так как только ОС может изменять значения сегментных регистров, то в определенной степени контролируется, какие сегменты пользовательская программа может использовать и разделять с другими программами. Поскольку эффективный адрес содержит только идентификацию записи таблицы сегментов и смещение адреса, постольку эффективный адрес имеет меньше разрядов, чем виртуальный. Именно благодаря тому, что виртуальный адрес не ограничен размером регистров процессора, 32-разрядный процессор с 32-разрядным виртуальным адресом может поддерживать большее виртуальное адресное пространство. Но даже и в этом случае, эффективный адрес может адресовать лишь подмножество адресного пространства без перезагрузки ОС сегментных регистров. Кроме того, хотя виртуальный адрес может иметь длину более 32 разрядов, отдельная операция по-прежнему использует только 32 разряда адреса. Таким образом, ограничение в 4 ГБ по-прежнему сохраняется, независимо от того, сколько разрядов в виртуальном адресе. Это объясняет, почему даже системы, поддерживающие большие виртуальные адреса, переходят с 32- на 64-разрядные процессоры. Теперь сопоставим рассмотренную нами адресацию относительно сегмента с одноуровневой памятью AS/400. Одноуровневая память и виртуальные адреса располагаются ниже MI и не видны пользователю. Таким образом, для защиты адресов не требуется дополнительный уровень трансляции (эффективного адреса в виртуальный), она осуществляется с помощью указателей. Защищая указатели (с помощью разрядов тега), не надо идти на дополнительные накладные расходы, связанные с загрузкой и сохранением таблиц сегментов для каждой программы. Как уже упоминалось при обсуждении структуры объектов, в AS/400 одноуровневая память также разделена на сегменты. Важно то, что при использовании одноуровневой памяти большой адрес AS/400 (48 и 64-разрядный) позволяет программе ниже MI адресовать любой сегмент всего адресного пространства, а не только подмножество сегментов, как в модели адресации относительно сегмента. Программа может обращаться ко всей виртуальной памяти, а сама виртуальная память может быть разделяемой без каких-либо накладных расходов. Что такое одноуровневая память Прежде чем погрузиться внутрь одноуровневой памяти, давайте попытаемся осмыслить общую картину, рассмотрев ее концепции и компоненты. Затем обсудим, почему одноуровневая память столь важна для AS/400 и разберем некоторые детали ее работы, взяв в качестве примера программу, выполняющую последовательное чтение индексированного файла базы данных (READ на ЯВУ или FETCH в SQL). В рамках этого примера мы разберем использование нескольких объектов: программы, индекса, курсора, области данных и др. Некоторые из них находятся в памяти, а некоторые нет. Начнем с краткого обзора адресации этих и любых других объектов. Над MI нет различий между памятью и диском (или другим вспомогательным хранилищем). OS/ 400 работает только с объектами, их именами и открытым содержимым. MI работает со своими объектами — декомпозицией объектов OS/400 — с помощью их идентификаторов (указателей). Других способов задания объектов на уровне MI нет. Программы, курсоры, области данных и другие объекты могут быть найдены простым указанием их имени. Чтобы использовать объект как ресурс, исполняющейся программе нужно «знать» только его имя и тип (как Вы помните, указание библиотеки необязательно, так как если она не задана, то будет просматриваться список библиотек). Имя объекта сразу же отображается в виртуальный адрес. Виртуальные адреса всех поименованных объектов находятся в библиотеках. Данный адрес помещается в указатель в процессе операции разрешения (описывалась в главе 5). Таким образом, системный указатель содержит виртуальный адрес заголовка объекта, который, в свою очередь, может содержать указатели на другие части данного объекта OS/400 и связанных с ним объектов MI. Для обращения к данным объекта, или для исполнения команд программы, они должны быть перенесены в память. В нашем примере последовательного чтения базы данных, фрагмент программы, содержащий команды на выполнение чтения, должен быть перенесен с диска в память, прежде чем команды исполнятся. Такой перенос с диска в память происходит ниже уровня MI, так как MI не различает диск и память. Можно считать, что все объекты находятся в памяти. То, что размер физической памяти слишком мал для хранения всех объектов — ограничение современных аппаратных технологий. Когда требуется фрагмент объекта, которого в памяти нет, этот отсутствующий фрагмент переносится и замещает некоторую неиспользуемую часть памяти. Можно также для наглядности представлять себе память как набор экранов, используемых для просмотра огромного пространства, содержащего все объекты. Процесс переноса страниц в память и из нее тогда будет выглядеть как изменения изображений на одном или нескольких экранах. Рисунок 8.1 иллюстрирует отображение объектов на виртуальные адреса ниже уровня MI. Физическое расположение разных фрагментов объектов здесь показано на примере двух: программы и пространства. Для простоты восприятия даны очень маленькие объекты, но концепция неизменна для объектов любого размера. Кроме того, на рисунке изображены два основных компонента управления памятью SLIC: управление вспомогательной памятью и управление основной памятью. Вкратце, их функции таковы: управление вспомогательной памятью распределяет виртуальным адресам объекта дисковое пространство, а управление основной памятью руководит перемещениями между дисковой и основной памятью.

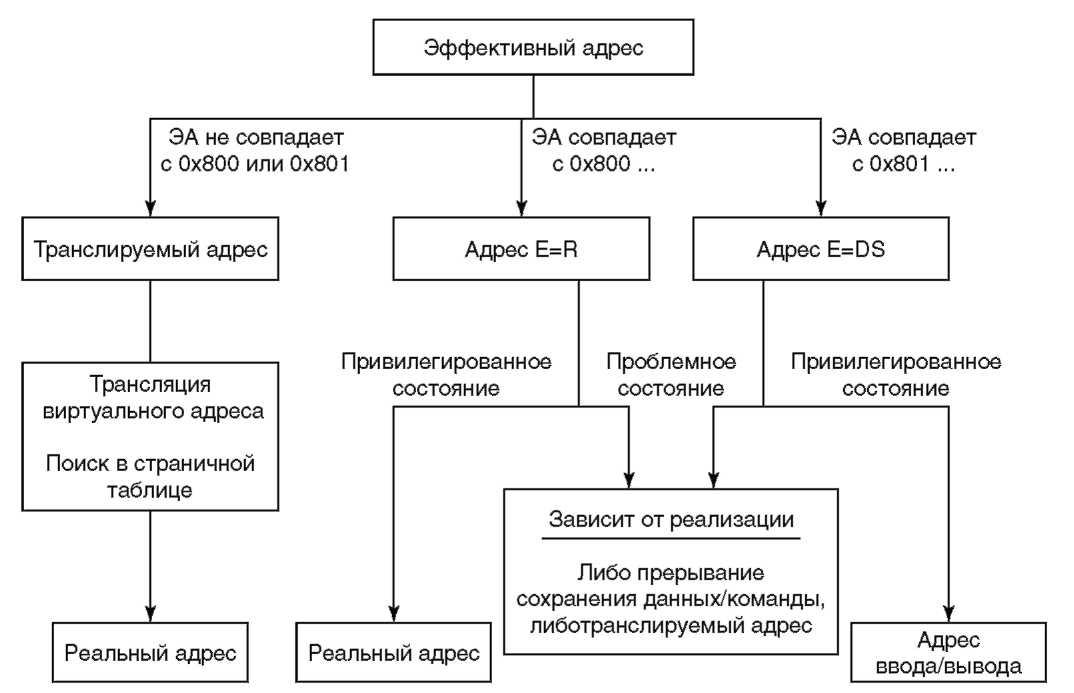

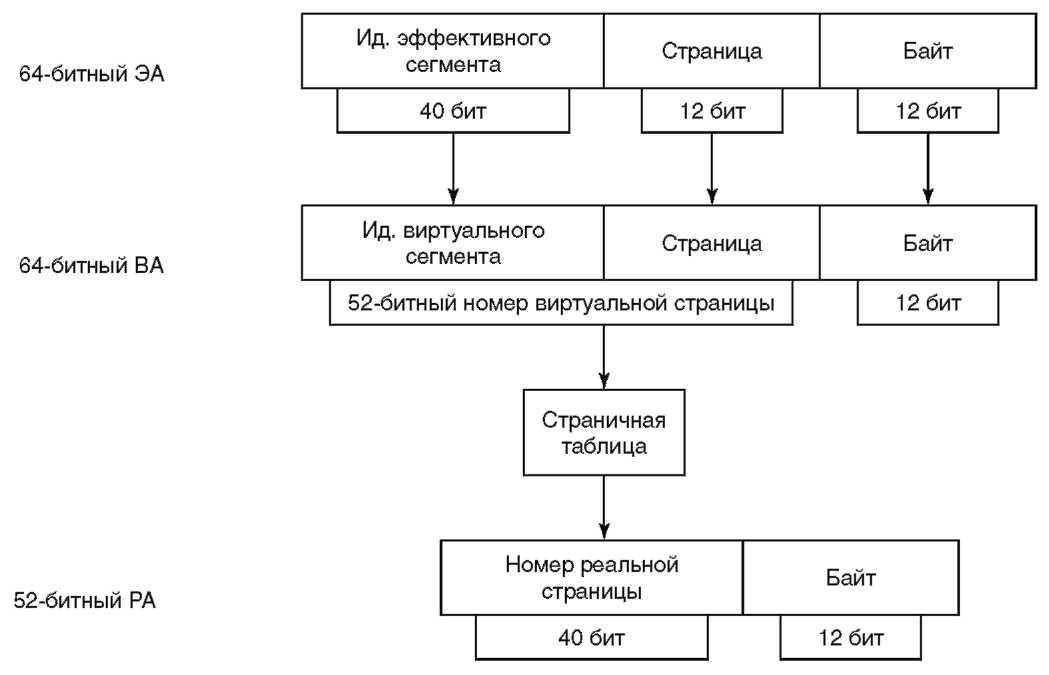

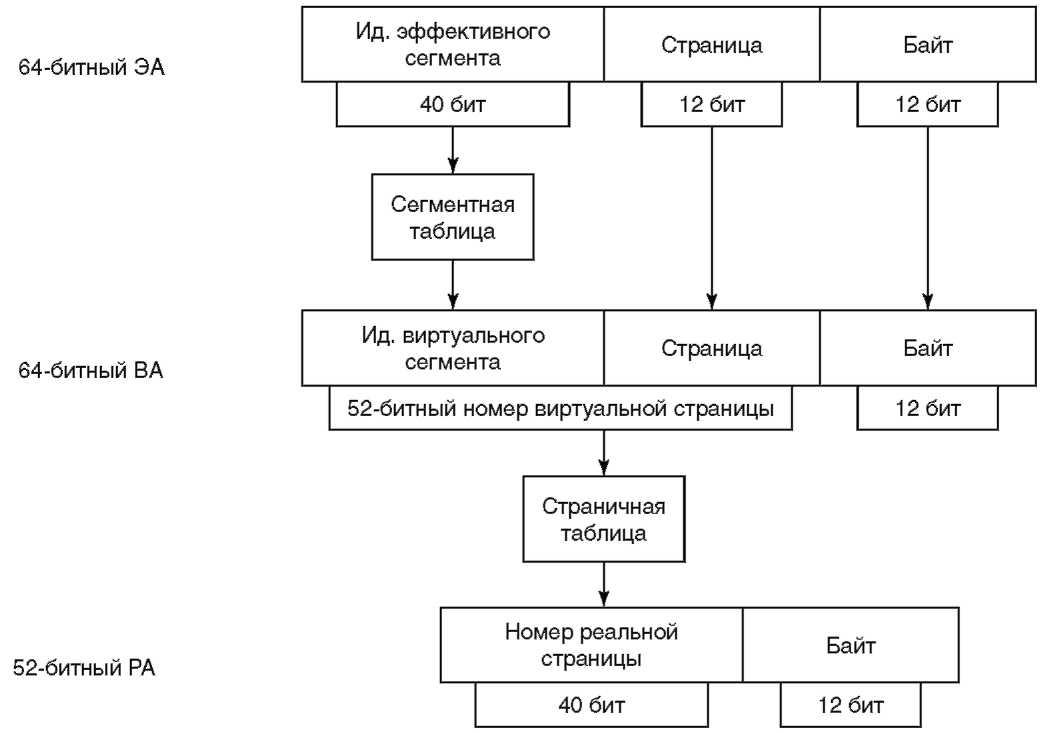

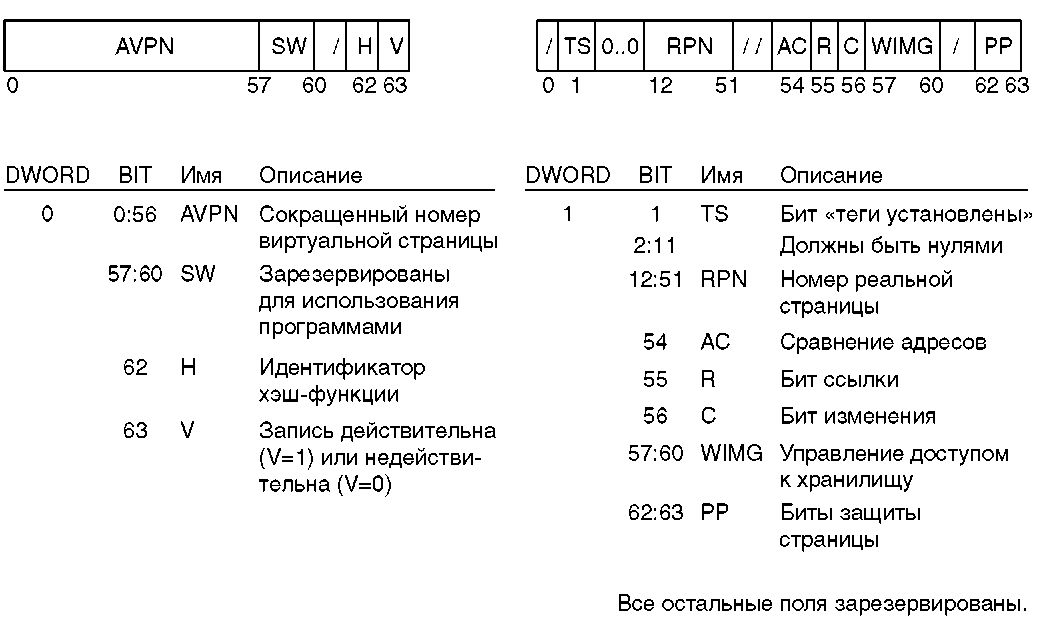

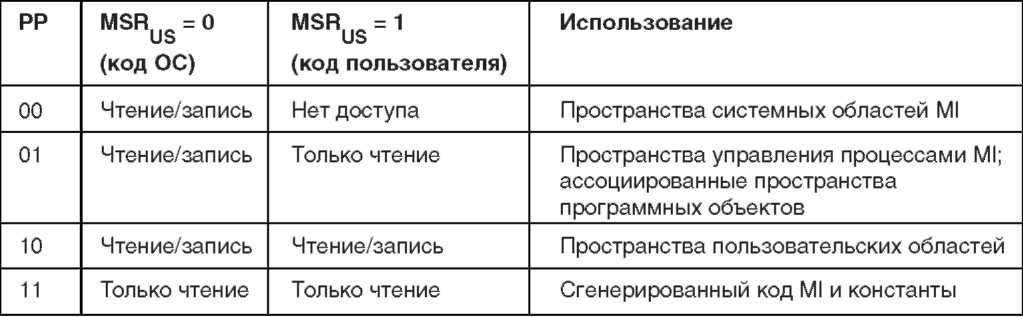

Рисунок 8.1. Объекты в одноуровневом хранилище На рисунке видно, что память состоит из соответствующих экранам из предыдущей аналогии, страничных фреймов (их называют так, потому что они содержат страницы), размер которых на машинах IMPI был равен 512 байтам, а теперь на PowerPC — 4 КБ (4 096 байтов). Объект на диске разделен на страницы того же размера, что и страницы памяти. Со страницей диска связан виртуальный адрес объекта. Он может обозначать любой байт в пространстве объекта, и следовательно, указывать в середину страницы. Большой объект может занимать несколько страниц, но система спроектирована так, что на странице не могут содержаться части более чем одного объекта. Удивительно, но мне часто задают вопрос: «Для чего нужна виртуальная адресация до байта? Почему не адресовать просто объекты, как это делают команды MI?». Для полного ответа, необходимо начать с того, что AS/400 (как CISC, так и RISC-мо-дели) работают на самых обычных процессорах, получающих команды и данные из памяти. Механизм адресации процессора, показанный на рисунке 8.1, ничего «не знает» об объектах. Системные объекты MI находятся в памяти, и процессор использует побайтную адресацию для получения информации о них: записей файла, команд программы и т. д. Процессор IMPI использует для доступа к памяти 48-разрядный виртуальный адрес, транслируя его в реальный; процессор PowerPC — эффективные адреса, которые транслирует сначала в виртуальные, а потом в реальные адреса. В обоих процессорах адреса следующей команды и используемых данных хранятся в аппаратных регистрах. Страница, перенесенная в память одним процессом (заданием), становится доступной любому другому. Множество заданий могут использовать команды программ совместно. Записи, считанные из базы данных последними, вероятно, все еще находятся в памяти. Объем дискового ввода-вывода значительно сокращается при многократном считывании одних и тех же записей. Предположим, что в нашем примере чтения базы данных используется индекс, разделяемый с другими пользователями системы. Если этот индекс был недавно считан одним из них, то часть или весь индекс, вероятно, все еще в памяти, и не нужно ждать выборки страниц индекса с диска. В обычной системе с более ограниченными возможностями разделения данных в память пришлось бы перенести новую копию индекса, несмотря на то, что одна там уже есть. Получив виртуальный адрес, аппаратура сначала проверяет, не присутствует ли уже соответствующая страница в памяти. Если она там, то она и используется. Если нет, то отсутствующая страница будет считана с диска. Трансляция виртуального адреса в реальный состоит в поиске в страничной таблице, расположенной в памяти, страничного фрейма, соответствующего виртуальному адресу. Аппаратный просмотр таблицы страниц в поисках группы записей PTEG (page table entry group) ведется с помощью алгоритма хеширования (описывается далее в этой главе). Каждая PTEG содержит восемь записей таблицы страниц, которые просматриваются по одной. Если заданная страница не найдена, то происходит страничная ошибка — аппаратное прерывание, по которому управление основной памятью SLIC определяет дисковый адрес, соответствующий виртуальному, и обращается к процессору ввода-вывода с просьбой прочитать страницу с диска. Для ускорения поиска страниц, использовавшихся последними, процессор содержит набор регистров, называемый справочным буфером трансляции TLB (translation lookaside buffer), где запоминаются последние использовавшиеся записи таблицы страниц. Так как регистры TLB встроены в процессор, то загрузка из памяти, где расположена таблица страниц, при обращении виртуальному адресу недавно использованной страницы, не требуется. Если же виртуального адреса в TLB нет, то на следующей стадии процесса трансляции аппаратура обращается к таблице страниц. Процессоры PowerPC, используемые в последних моделях AS/400, могут также работать в режиме неактивных тегов. Данный режим никогда не используется OS/400, но для полноты описания поговорим и о его адресации. Итак, если процессор PowerPC работает в режиме неактивных тегов, то аппаратура сначала обращается к справочному буферу сегментов SLB (segment lookaside buffer) — другому набору регистров микросхемы процессора, содержащему использованные последними фрагменты таблицы сегментов. Если совпадения в регистрах SLB не найдено, то аппаратура обращается к таблице сегментов в памяти перед тем, как обратиться к регистрам TLB и таблице страниц. Другими словами, в режиме неактивных тегов процесс трансляции адресов трехшаговый: эффективный — виртуальный — реальный. Для сообщения процессору ввода-вывода о страничной ошибке SLIC использует адрес другого типа, называемый адресом прямого сохранения (direct store address). Такие адреса употребляются при взаимодействии с любым внешним устройством. Они начинаются с шестнадцатиричного значения 801. Часть адреса прямого сохранения передается непосредственно процессу, управляющему внешним устройством. Когда страница переносится с диска, она замещает в памяти страницу, которая давно не использовалась. С любой страницей связаны специальные разряды, которые устанавливаются при каждом обращении к ней. Измененные страницы также помечаются, чтобы в случае замещения в памяти они были записаны обратно на диск. Память содержит команды программ, данные и указатели. Под данными здесь понимается все, что не является исполняемой командой или указателем: все объекты OS/400, кроме объектов-программ, а также неисполняемые части объектов-программ. Сравните этот подход с подходом команды «WRSYSSTS» (Work With System Status), которая различает только страничные ошибки, связанные с работой базы данных, и все остальные. Страничные ошибки базы данных относятся только к физическим и логическим файлам. Прочие страничные ошибки, такие как ошибки для программы, курсора или любого пространства из нашего примера последовательного чтения относятся ко все остальным. Ранее мы рассмотрели страничные ошибки. Для считывания страницы с диска не обязательно ждать, пока такая ошибка произойдет. Любой компонент SLIC или любая транслированная программа MI может запросить у управления главной памятью SLIC явный перенос (считывание) в память диапазона виртуальных страниц (одной или более). Функционально явный перенос страниц в память не нужен, так как требуемые страницы всегда будут перенесены по страничной ошибке, но тогда процесс, вызывавший ее, ожидает завершения чтения с диска. Запрос на операцию переноса до того, как страницы фактически потребуются, позволяет выполнять операции дискового чтения параллельно с другой обработкой. Таким образом, явные переносы снижают временные затраты и повышают производительность. Возможно также явное создание очищенных страничных фреймов в памяти. Запрос на очистку, переданный управлению главной памятью, расписывает один или несколько страничных фреймов в памяти двоичными нулями. Эта операция полезна, например, в тех случаях, когда буфер заполняется новыми данными и текущее содержимое диска Вас не интересует. Вместо чтения страниц буфера, как в результате отдельных страничных ошибок, так и с помощью переноса, операция очистки позволяет обнулить страничные фреймы без обращения к диску. При запросе на перенос или очистку может быть выбран параметр обмена. Он задает диапазон виртуальных страниц, которые компонент управления главной памятью SLIC может использовать для замещения вместо выбранных по нормальному алгоритму. Обмен применяется для того, чтобы не удалять из памяти страницы, к которым постоянно обращаются, и не заменять их страницами, которые вряд ли будут нужны больше одного раза. Обмен полезен и в том случае, когда значительное число страниц переносится в небольшую память или небольшой пул памяти. (Память часто разделяется на несколько пулов меньшего размера и вся подкачка страниц для данного процесса выполнятся в одном пуле. Подробнее о пулах — в главе 9.). В запросе на перенос или очистку также можно указать, что одну или несколько страниц следует зафиксировать в памяти. Фиксированная страница становится резидентной и не будет удалена из памяти или записана обратно на диск вплоть до отмены этого распоряжения. Некоторые структуры данных SLIC, такие как элементы диспетчеризации, используемые в управлении процессами, всегда резидентные. Для ввода-вывода на виртуальную страницу и обратно, они должна быть зафиксированы, так как при перемещении данных по шине ввода-вывода используется реальный адрес фрейма страницы. Режим фиксации снимается отдельным запросом к управлению памятью. Дополняет перенос и очистку страниц возможность сбросить (переписать) одну или нескольких страниц на диск. Сброс имеет смысл только тогда, когда страница в памяти были изменена, то есть копия страницы на диске неактуальна. В отличие от переноса и очистки, которые не являются функционально необходимыми (эти задачи выполнит обработка страничной ошибки), сброс иногда необходим, например, при журналировании базы данных. В этом случае компонент базы данных в SLIC должен гарантировать, что записи журнала в журнальном пространстве записаны на диск, причем он обязан использовать функцию сброса, не дожидаясь, пока страницы журнального пространства будут записаны на диск в результате страничных ошибок. Кроме того, сбросом можно снять фиксацию в памяти одной или нескольких страниц. Наконец, страничные фреймы могут быть удалены из памяти без записи обратно на диск. Функциональных причин для удаления страниц нет, но это полезно, так как устраняет последующие операции записи на диск, например, если буфер памяти был опустошен и данные в нем больше не нужны. Процессор PowerPC имеет отдельные кэши данных и команд, играющие роль буфера между основной памятью и процессором. По сути дела кэши — это регистры на микросхеме процессора, обеспечивающие быстрый доступ к недавно использовавшимся командам или данным. В AS/400 часть виртуальных адресов используется для доступа к кэшам. Указатели должны быть защищены от повреждений. Программа пользователя, работающая на уровне MI, вполне способна изменить указатель, так как указатели хранятся в ассоциированном пространстве объектов MI вместе с другими структурами, к которым программа должна иметь доступ. Значения указателей также могут быть разрушены физическими явлениями, такими как флуктуации напряжения. Если указатель изменен «незаконно» (то есть не процедурой SLIC с помощью команды, недоступной непосредственно в MI), а каким-либо иным способом, то аппаратура сбрасывает разряд тега, делая тем самым указатель недействительным. Все временные и постоянные объекты подлежат страничному обмену (переносу их на диск и обратно в память по мере необходимости). Некоторые структуры (таблица страниц) и программы SLIC не откачиваются; они загружаются в процессе IPL и должны находиться в памяти постоянно. Их адреса не требуют трансляции, так как виртуальные адреса подобных структур или команд — реальные адреса памяти. Такого рода адреса всегда начинаются с шестнадцатиричного 800. Теперь, после краткого обзора, перейдем к детальному рассмотрению этих тем: разберем подробно влияние одноуровневой памяти на производительность, работу указателей, трансляцию адреса, и, наконец, управление дисками. Внимание! Для индикации «горячих» тем, будет использоваться «перечная» система. Одноуровневая память и производительность Как уже отмечалось, основное достоинство одноуровневой памяти — в сокращении числа команд, требуемых для выполнения определенных функций ОС. Можно привести множество примеров функций, производительность которых повышается благодаря одноуровневому хранилищу. Значительно упрощается за счет ненужности перемещения файлов файловая система, эффективней работает база данных. Но одно преимущество сразу бросается в глаза — это резкий рост производительности AS/ 400 при работе в интерактивном режиме, непосредственно зависящей от времени на переключение процессов. Рассмотрим пример, иллюстрирующий, как переключение процессов влияет на общую производительность AS/400. В обычной ОС, использующей адресацию относительно сегмента, при переключении процессов требуется изменение содержимого сегментных регистров. Если этого не сделать, то меньшие эффективные адреса в новой программе будут ошибочно транслироваться в виртуальные, принадлежащие программе предыдущего процесса. Проблема возникает потому, что каждый процесс в системах такого типа имеет собственную эффективную память, которая начинается с адреса 0. Данный тип адресации используется большинством современных версий Unix, а также AIX IBM. Роль сегментных регистров в системах такого типа — в отображении эффективных адресов в виртуальную память большего размера. Для этого содержимое сегментных регистров должно сохранятся где-то в памяти при всяком переключении с данного процесса на другой, и снова восстанавливаться, когда первый процесс опять начинает выполняться. Использование в процессорах PowerPC таблицы сегментов вместо сегментных регистров делает ненужным сохранение содержимого регистров в памяти — там уже и так находится таблица сегментов. Однако при переключении процессов необходимо очистить регистры SLB от информации предыдущего процесса. При трансляции эффективных адресов в виртуальные с использованием таблицы сегментов, регистры SLB обновляются по одному. Использование таблицы в памяти до заполнения всех регистров SLB может привести к увеличению числа тактов процессора на каждое обращение к памяти. В результате, производительность процесса снизится, пока не будет загружено некоторое число регистров. Если, например, процесс, на который происходит переключение — последовательное чтение из базы данных, потребуется протранслировать, по крайней мере, четыре адреса (по одному для программы, индекса, курсора и пространства данных) лишь для того, чтобы начать работу. Более того, так как каждый из таких объектов имеет несколько сегментов (со своими виртуальными адресами), вероятно, потребуется протранслировать с помощью таблицы в памяти от 8 до 12 адресов, прежде чем регистры SLB можно будет эффективно использовать. Как мы уже говорили, одноуровневая память AS/400 не использует ни таблицу сегментов, ни регистры SLB. Эффективный адрес соответствует виртуальному, и никакого преобразования не требуется, так как вся виртуальная память адресуется программой напрямую. Следовательно, при переключении процессов не происходит спада производительности, связанного с таблицей сегментов. И это еще не все! Возьмем трансляцию виртуального адреса в реальный с помощью таблицы страниц. В обычной системе каждый пользовательский процесс может иметь свою собственную виртуальную память с уникальной таблицей страниц. Пример — Microsoft Windows NT. В этой ОС компонент управления памятью предоставляет каждому процессу большое отдельное виртуальное адресное пространство. Это означает, что при переключении процессов нужно не только изменить таблицу страниц, чтобы обеспечить корректное отображение адресного пространства нового процесса, но также и очистить все регистры TLB. После переключения процессов адреса транслируются из виртуальных в реальные с помощью новой таблицы страниц, и содержимое регистров TLB обновляется по одному. Подобно перезагрузке регистров SLB, перезагрузка регистров TLB после переключения процессов снижает производительность. В AS/400 только одна виртуальная память, поэтому имеется только одна таблица страниц, которую используют все. Следовательно, при переключении процессов не нужна очистка TLB, и размер TLB больше, чем у других систем. Регистры TLB содержат использованные последними записи таблицы страниц. С течением времени самые старые записи заменяются новыми. При большем числе регистров выше вероятность того, что виртуальный адрес, транслированный в отдаленном прошлом, все еще будет в TLB. TLB большего размера означает, что при повторном переключении на ранее выполнявшийся процесс, некоторые или все его адреса уже доступны, что невозможно, если регистры TLB очищать при всяком переключении процессов. И здесь единая виртуальная память AS/400 позволяет сохранить значительный объем процессорного времени. Наконец, современные процессоры не выбирают информацию из памяти и не записывают ее туда непосредственно. Кэш-память содержит порции основной памяти и имеет собственный справочник. В зависимости от архитектуры кэш-памяти на данном компьютере и от того, есть ли разряды виртуального адреса в справочнике кэша, при переключении процесса может потребоваться очистка кэша. А при использовании одноуровневой памяти это не нужно. Операционные системы, предназначенные для работы с обычной виртуальной памятью, чаще всего пытаются избежать большого числа переключений процессов из-за неизбежных накладных расходов. Но если это не удается, для эффективной работы таким системам нужен высокопроизводительный процессор. По сравнению с другими системами, переключение процессов на AS/400 выполняется очень быстро, так как требует лишь нескольких действий. Спад производительности при старте нового процесса в AS/400 также не столь резкий. В результате, части как OS/400, так и SLIC, спроектированы для выполнения большого числа переключений процессов. Несколько лет назад сотрудники подразделения IBM Research обнаружили в ходе исследований, что в типичной пользовательской среде AS/400 переключение процессов происходит примерно через каждые 1200 команд. В это даже трудно поверить, ведь некоторым системам нужно выполнить 1000 или более команд только для самого переключения процессов. Но не AS/400! Благодаря способности быстро переключаться между процессами, производительность AS/400 в интерактивном режиме очень высока. Еще System/38 и первые AS/ 400 были оптимизированы для интерактивных приложений обработки транзакций. К AS/400 могут быть подключены любые терминалы. Одна такая большая система легко может поддерживать несколько тысяч параллельных пользователей, далеко превосходя в этом своих конкурентов, таких как Unix или Windows NT. Работая с приложениями, требующими частых переключений процессов, AS/400 способна превзойти по производительности системы с более быстрыми процессорами, так как выполняет меньше команд. Теперь рассмотрим среду, не требующую частых переключений процессов, например, среду пакетной обработки, где один процесс исполняется в течение долгого времени. Здесь скорость переключения процессов не играет существенной роли. Ранние системы AS/400 не очень хорошо работали в пакетном режиме — сказывалась недостаточная производительность процессора[ 64 ]. Дело в том, что в ранних версиях рочестерских систем никогда не использовались высокопроизводительные процессоры. Доходило даже до того, что при описании характеристик различных моделей AS/400, не указывались скорости процессоров в MIPS (миллион команд в секунду) или МГц. Подобно тому, как MIPS указывает, сколько команд процессор может выполнить в секунду, МГц задает число тактов за секунду. Если два разных процессора должны для выполнения одной и той же задачи выполнить одинаковое количество команд, и по всем остальным параметрам наблюдается такое же равенство, то значения MIPS или МГц могут дать некоторое представление о производительности процессоров. Но если для выполнения одной и той же работы процессорам нужно разное число команд, то ни MIPS, ни МГц не имеют никакого значения. В Рочестере всегда настаивали на оценке объема работ, который может выполнить AS/400, в таких показателях, как число транзакций в секунду. Лаборатория IBM в Ро-честере — лидер в создании промышленных тестов для обработки транзакций. Здесь в тесном контакте с Transaction Processing Performance Council измеряются показатели TPC для вычислительных систем. Эти показатели также призваны отражать стоимость каждой транзакции, рассчитанную на основании цен на аппаратуру и ПО для данной конфигурации. Все это дает пользователю возможность сравнивать разные вычислительные системы как по цене, так и по производительности. Так вот, в соответствии с этими тестами, AS/400 — один из лидеров как по показателю цена/производительность, так и по чистой производительности. Да и что здесь удивительного — ведь она создавалась именно для решения задач такого типа. Интерактивная обработка подразумевает присоединение к AS/400 терминалов, таких как 5250. Такие функции, как обновление полей на экране требуют много переключений процессов, особенно в случае подключения сотен или тысяч терминалов. При переходе в начале 90-х годов к клиент/серверным вычислениям, большая часть экранной обработки стала выполняться на ПК (клиент). Тем самым число переключений процессов на AS/400 (сервер) сократилось. Но многие характеристики клиент/серверных вычислений по-прежнему напоминают интерактивную обработку. Когда сотни или тысячи пользователей одновременно нажимают клавиши на клавиатуре или щелкают мышью, обращаясь к базе данных и ожидая затем ответа, быстрое переключение процессов AS/400 просто необходимо. AS/400 гармонично сочетает одновременную поддержку многочисленных пользователей (процессов) с требованиями клиент/серверной среды к пересылке данных. Но есть серверные приложения, специально предназначенные для интенсивных вычислений. Пример — приложения для поддержки принятия решений, где для генерации отчета требуется анализ больших объемов данных. Пользователи могут создавать сложные запросы, спрашивать «что если», выполнять поиск взаимосвязей в данных и т. д. Для такого приложения необходим тип обработки, больше похожий на пакетную, чем на интерактивную среду. Для таких серверных приложений AS/400 были нужны мощные процессоры. И вот, несколько лет назад мы впервые представили специальные модели AS/400, предназначенные именно для высокопроизводительных серверов. В этих моделях мощные процессоры и большая память. Результаты различных клиент/серверных тестов показывают, что модели Advanced Server весьма конкурентоспособны, как по цене, так и по производительности. Не удивительно, что многие заказчики признали их лучшими и для обычных пакетных приложений. Переключение процессов интенсивно используется как в интерактивных, так и в клиент/серверных приложениях. Быстрое переключение процессов всегда лучше медленного. Путем сокращения числа необходимых команд одноуровневая память повышает производительность не только переключения процессов, но и ряда других функций. Вернемся, например, к уже обсуждавшейся операции с файлами. Обычный сервер многократно выполняет операции открытия-закрытия файлов, что ведет к повышенной дисковой активности и снижает общую производительность системы. AS/400 обрабатывает такие файлы «на месте», устраняя излишние накладные расходы. Производительность процессора важна, но следует помнить, что каждая команда, которую не нужно выполнять, эквивалентна наличию для этой команды процессора с бесконечной скоростью. RISC-процессоры быстры, но не настолько. Указатели и теги После роста производительности, самое большое достоинство одноуровневой памяти — всеобъемлющая возможность совместного доступа. Впрочем, это и самый большой ее недостаток. Если каждый пользователь системы имеет доступ к большому единому адресному пространству, требуются гарантии от несанкционированного доступа к тем объектам или информации, на которые у этих пользователей нет прав. В главе 5 мы говорили, что такая защита осуществляется в AS/400 указателями. Давайте теперь рассмотрим указатели и их функции более подробно. Итак, доступ к объекту MI обеспечивается путем разрешения указателя. Указатели имеют длину 16 байт (128 бит). Разрешенный системный указатель содержит возможность прямой адресации системного объекта, то есть в нем находится 64-разрядный виртуальный адрес. Указатели других типов (пространства, данных, команд и процедур) также содержат виртуальные адреса. Указатели находятся в ассоциированном пространстве системного объекта. В этом же пространстве содержатся данные, к которым имеет доступ и которые может изменить программа MI. Доступ и модификация данных в ассоциированном пространстве законны; изменение указателя — нет. Если бы программа MI могла изменять содержимое указателя, то была бы нарушена защита. Адрес в указателе мог бы быть изменен так, чтобы указывать на еще какой-нибудь объект или структуру, доступ к которой запрещен. Конечно, все это касается пользовательских программ, в которых команды MI заданы непосредственно; и не имеет отношение к программам на ЯВУ, таких как RPG или Cobol. Когда разрабатывалась структура указателя, способами защиты были избраны устранение ассемблера MI, перевод некоторых команд в разряд привилегированных и удаление из указателей полномочий. Как говорилось в главе 7, все эти усиления уровней защиты привносились в AS/400 с течением времени. Но даже такая степень защищенности не дает стопроцентной уверенности в том, что содержимое указателя не подвергнется несанкционированным изменениям. В главе 5 отмечалось, что ассоциированное пространство, содержащее указатели, занимает отдельный сегмент системного объекта. Первоначально в System/38 мы хотели использовать два сегмента: один — для данных, а второй —для указателей. Но такой подход снижал производительность системы. При использовании объекта было необходимо считывать с диска страницы, как сегмента данных, так и сегмента указателей, что повышало накладные расходы. Кроме того, два сегмента требовали некоторого увеличения размеров памяти. Единственным плюсом ассоциированного сегмента указателей была надежда, что он может защитить указатели от модификации пользователями. Но оказалось, что это не так. Скоро выяснилось, что мы не можем защитить ассоциированный сегмент указателей от изменений. При той степени защиты, которая планировались для System/38 (уровень 30), пользователь, имевший право доступа к объекту, мог работать с его содержимым с помощью ассемблера MI. Помещение указателей в отдельную часть объекта не предоставляло дополнительной защиты. Пришлось искать другое решение. Аппаратная защита указателей

Мы понимали, что необходима некоторая форма аппаратной защиты памяти для указателей. Многие из больших систем того времени, такие как System/370, использовали для защиты памяти специальные аппаратные разряды, разрешавшие или запрещавшие пользователю доступ к некоторому блоку байтов памяти. Биты защиты обычно помещались в отдельном аппаратном массиве памяти, где пользователь не мог до них добраться. При каждом обращении к памяти этот массив проверялся, чтобы определить, имеет ли пользователь право на доступ к данному блоку памяти. Обычно такая защита устанавливалась на физический блок памяти размером в одну страницу. Первоначально использовать в аппаратуре System/38 такой тип защиты памяти не планировалось: никто не думал, что он понадобится, ведь защита проектируемой системы выполнялась на уровне объектов. Однако, когда стало понятно, что некая форма аппаратной защиты все же нужна, мы рассмотрели возможность защиты блока размером в одну страницу. Но, во-первых, это было дорого, а, кроме того, такой подход не вполне соответствовал планам разработчиков. В идеале, нам виделась защита для каждых 16 байтов памяти, так как указатель занимает именно столько. Но чтобы сделать систему производительной, хотелось иметь возможность размещать указатели где угодно, но тогда отдельный аппаратный массив разрядов защиты для каждых 16 байтов памяти становился неприемлем по стоимости. Наконец, нашлось решение: использовать для защиты памяти дополнительные разряды, предназначенные для кода коррекции ошибок ECC (error correcting code). Иногда, в памяти компьютера возникают ошибки из-за перепадов напряжения в электросети или по другим причинам. Для защиты от ошибок в большинстве памятей используются коды обнаружения ошибок и коды исправления ошибок. Действуют они так: к каждому слову памяти добавляются дополнительные разряды. Слово памяти содержит столько разрядов, сколько может быть считано за одну операцию. При считывании данных из памяти эти дополнительные разряды проверяются, чтобы определить, не произошла ли ошибка. Простейшая форма обнаружения ошибок — добавление к слову памяти одного разряда четности. Его значение выбирается так, чтобы число разрядов 1 в слове памяти, включая разряд четности, всегда было четным. Если в памяти происходит ошибка, вызывающая изменение значения любого из битов с 1 на 0 или наоборот, то она будет обнаружена, когда при следующем считывании слова окажется, что число разрядов 1 нечетно. Четность позволяет определить одиночную ошибку, но не говорит, в каком разряде она произошла. С помощью такого механизма, обычно применяемого на ПК, можно определить нечетное число ошибок в слове памяти. Но если число ошибок четное, он не поможет. Большинство компьютеров, используемых для коммерческих задач, в частности AS/400, как для обнаружения, так и для исправления ошибок применяют дополнительные разряды кодов коррекции. Эти дополнительные разряды могут определять все однократные и многократные ошибки, и даже указать, в каком именно разряде они произошли. Таким образом, аппаратура может исправить ошибку и продолжить работу. Значение коррекции ошибок очевидно для каждого, кому приходилось видеть на экране ПК сообщение «memory parity error». С таким сломанным ПК ничего нельзя сделать до тех пор, пока неисправный модуль памяти не заменен. По этой причине многие старшие модели современных ПК используют памяти ECC. Оригинальная аппаратура System/38 имела 32-разрядное (4-байтовое) слово памяти. ECC требовал дополнительных 7 разрядов, то есть для каждого слова памяти было нужно 39 разрядов. Технология тогда позволяла увеличивать размер слова только приращениями по 8 разрядов, то есть, фактически, слово памяти имело размер 40 разрядов. Для каждого 4-байтового слова памяти предусматривался дополнительный разряд, который и должен был осуществлять функции защиты памяти. Мы назвали его разрядом тега. Указатель занимает 16 байтов памяти. Мы решили всегда помещать указатели на 16-байтовые границы (все четыре младшие разряда адреса памяти равны 0). Такую конфигурацию обычно обозначают термином четверное слово (quadword), или, иначе говоря, 16-байтовое поле, выровненное на 16-байтовую границу. Есть и двойные слова, а кроме того, слова, выровненные на 8-ми и 4-байтовые границы. Обычно, под термином слово понимается 4 байта. Указатель в оригинальной System/38 занимал четыре последовательных 4-байтовых слова памяти, каждое со своим разрядом тега. Мы решили, что для каждого слова памяти этот разряд будет равен 1, если слово содержит любую из четырех частей указателя; и 0 — если не содержит. Для самого указателя нужен только один разряд, так что если все четыре разряда в четырех последовательных словах памяти установлены в 1, то значение логического тега указателя равно 1. Если любой из четырех разрядов был равен 0, то и логический тег указателя равнялся 0. Последующие версии AS/400 имеют 64-разрядное (8-байтовое) слово памяти. Такое слово требует 8 разрядов ЕСС; так что с учетом разряда тега, слова памяти AS/ 400 упакованы по 73 разряда. Мы по-прежнему размещаем указатели на 16-байтовых границах, и у каждого указателя есть один логический разряд тега. Если в AS/400 с 64-разрядным словом, два разряда тега в двух последовательных словах, содержащих указатель, оба равны 1, то и логический тег указателя равен 1. Если же любой из разрядов равен нулю, то и указатель имеет логический тег 0. Чтобы оставаться в рамках принятой терминологии, мы называем 64-разрядное слово памяти двойным словом. Всякий раз, когда в AS/400 происходит запись в память, аппаратура управления памятью строит ЕСС и сохраняет его вместе со словом памяти. В процессе операции записи эта аппаратура также отключает разряд тега в слове памяти (устанавливает его в 0). Так что в результате выполнения любой стандартной команды записи в память, разряды тега записанных слов всегда будут сброшены в 0. Режим активных тегов

В главе 2 мы говорили о расширениях архитектуры PowerPC. Одно из таких расширений — режим активных тегов. Когда процессор PowerPC работает в данном режиме, доступны дополнительные команды, которых нет в режиме неактивных тегов. Всего для AS/400 было добавлено 25 команд, доступных только в режиме активных тегов. Сюда входят команды множественной загрузки и сохранения четверных слов в регистрах, а также команды, обратные им. Есть также команды десятичной арифметики, системные функции вызова/возврата и команды выделения для проверки значений разрядов в управляющих регистрах. Шесть новых команд поддерживают теги. Некоторые из этих специальных теговых команд используются для установки или проверки значений разрядов тега. Одна из них, команда «Сохранить четверное слово» («stq»), сохраняет в памяти 16 байтов данных из двух 64-разрядных регистров и включает два разряда тега. Другая —«Загрузить четверное слово» («lq»), загружает 16 байтов памяти в два 64-разрядных регистра и устанавливает разряд в регистре управления в 1, если оба теговых разряда в считанных словах равны 1 (в противном случае этот разряд устанавливается в 0). Еще одна команда позволяет считывать теги из памяти в специальный регистр процессора. Использование этой команды будет рассмотрено в следующем разделе. Теговые команды: используются только в SLIC; они не генерируются транслятором для программ MI. Это означает, что любое сохранение в памяти, сгенерированное для программы MI, всегда использует стандартные команды и отключает разряды тега. Когда в процессе разрешения создается указатель, SLIC строит его в двух 64-разрядных регистрах и использует команду «stq» для включения теговых регистров в памяти. При всякой попытке использовать указатель программой MI, SLIC загружает его содержимое командой «lq» в регистры и затем проверяет, установлены ли разряды: тега. Если разряды тега сброшены, значит, кто-то изменил указатель, и он теперь неверен. Разряды тега AS/400 не предотвращают изменения указателей, а лишь определяют, производились ли эти изменения. Такой подход отличается от большинства схем защиты памяти. Обычно, защита памяти не допускает изменений, и такая защита на уровне страниц в AS/400 имеется. Однако указатели распознают лишь уже произошедшие модификации, что по сравнению с ранними версиями системы сокращает объем аппаратуры, но по-прежнему обеспечивает нужный уровень защиты. Указатели нельзя подделать. Теги гарантируют, что указатель создан ОС (SLIC), и что он не изменялся чем-либо, кроме SLIC. Недобросовестный пользователь, попытавшись создать, скопировать или изменить указатель, не сможет включить разряды тега и получит в результате бесполезные 16 байт. Именно поэтому AS/400 всегда работает в режиме активных тегов, несмотря на то, что процессоры PowerPC, используемые в ней, могут действовать и в режиме неактивных тегов. Указатели и теги на диске

Разработчики System/38 столкнулись с и другой проблемой. Допустим, потребуется переместить страницу из памяти на диск. В памяти есть дополнительные разряды для ЕСС и тегов, а на диске нет. Там используется другая форма кода коррекции ошибок, называемая циклическим избыточным контролем CRC (cyclic redundancy check), который не добавляет дополнительных разрядов к каждому слову памяти. Значит, нужен способ сохранения разрядов тега вместе с указателями при перемещении страницы, содержащей указатели, на диск. Короче говоря, нужно найти дополнительное место на диске. Магнитный диск представляет собой набор плоскостей, имеющих по две поверхности для записи. Поверхность каждого диска разделена на концентрические окружности, называемые дорожками. В свою очередь, дорожки разделены на сектора, которые и содержат информацию. Размер сектора для System/38 и AS/400 равен 520 байтам. Каждый сектор содержит 8-байтовый заголовок сектора и область данных в 512 байт. Размер сектора был выбран так, чтобы 512-байтовая страница System/38 умещалась в него. В System/38 было определено несколько специальных команд IMPI для работы с тегами. Одна из таких команд— «Извлечь теги» — использовалась для сбора тегов со страницы памяти. При записи страницы на диск, теги также записывались на диск. Другая команда IMPI — « Вставить теги»— применялась для помещения тегов обратно в память после считывания страницы с диска. Многие ISV и пользователи, знавшие о разрядах тега System/38, считали, что они хранятся на диске в 8-байтовых заголовках секторов. Но это не так. Информация на самой странице сохранялась в 512-байтной области данных сектора. Заголовок сектора содержал информацию о странице, но наиболее важной его задачей было хранение виртуального адреса страницы. Этот адрес нужен был для восстановления. Даже в случае потери таблицы в памяти, связывавшей виртуальные адреса с местами на диске, она могла быть восстановлена: достаточно считать заголовки каждого сектора и определить, с каким виртуальным адресом этот сектор связан. Так что большая часть пространства в заголовке сектора была занята виртуальным адресом страницы, места для тегов не оставалось. Это подтверждает простой расчет. Одна страница может содержать 32 указателя (16 байтов Г32 = 512), что означает 32 бита тегов на страницу. Виртуальный адрес в System/38 занимал 48 разрядов, но для идентификации страницы использовались не все из них. Младшие 9 разрядов виртуального адреса задавали байт на 512-байтной странице (29 = 512). Следовательно, для уникальной идентификации страницы нужно хранить только 39 старших разрядов виртуального адреса (48 — 9 =39). Однако даже без разрядов состояния потребовался бы минимум 71 разряд для хранения виртуального адреса страницы и всех битов тега (39 +32 =71), в заголовке же сектора было только 64 разряда. Хранить биты тега в заголовках секторов оказалось невозможно. Разработчики System/38, проявив недюжинную смекалку, нашли для тегов место внутри страницы. Дело в том, что некоторое пространство в указателе не используется. Если на странице есть хотя бы один указатель, то есть и некоторое неиспользуемое пространство, в котором можно хранить биты тега. Если указателей на странице нет, то все биты тега для нее равны 0, поэтому и хранить их незачем. Заголовок сектора в System/38 содержал информацию о том, есть ли на странице теги, и если есть, то где именно. До появления RISC-процессоров мы продолжали использовать на AS/400 и размер страницы, равный 512 байтам, и только что описанный метод хранения битов тега. Но уже несколько лет нас мучило желание увеличить размер страницы. Размер страницы в 512 байт был выбран для System/38 по причине ограниченности размеров основной памяти[ 65 ]. Но для увеличенной памяти AS/400 512-байтовая страница была слишком мала, страниц получалось слишком много, и таблицы страниц достигали гигантских размеров. Кроме того, уже многие годы мы «упаковывали» маленькие страницы в «логические» страницы большего размера для сокращения объема дисковых операций. Для новых процессоров было решено увеличить размер страницы до 4 КБ (4 096 байтов). В новых моделях был сохранен размер сектора на диске в 520 байт. Четырехкило-байтовая страница теперь хранится в восьми последовательных секторах. При наличии восьми 8-байтовых заголовков на каждой странице в 4 КБ больше чем достаточно места для хранения 256 теговых битов. Для извлечения тегов из памяти к архитектуре процессора PowerPC был добавлен специальный регистр тегов. Когда процессор выполняет специальную теговую команду, «Множественная загрузка двойных слов» («lmd»), в 16 регистров может быть считано из памяти до 16 двойных слов (восемь четверных слов). При выполнении команды в регистре тега сохраняется восемь теговых регистров четверных слов памяти. Обратите внимание, что в регистре тега сохраняются 8 логических битов тега, а не 16 физических, как в памяти. Вспомним, что четверное слово это два 64-разрядных (8-байтовых) слова памяти; следовательно, в четверном слове два физических бита тега, так что в восьми четверных словах — 16 физических битов тега. С помощью команды «lmd» биты тегов страницы могут быть собраны для последующей записи на диске вместе с данными. Эта команда также доступна только в режиме активных тегов. Внутри указателя

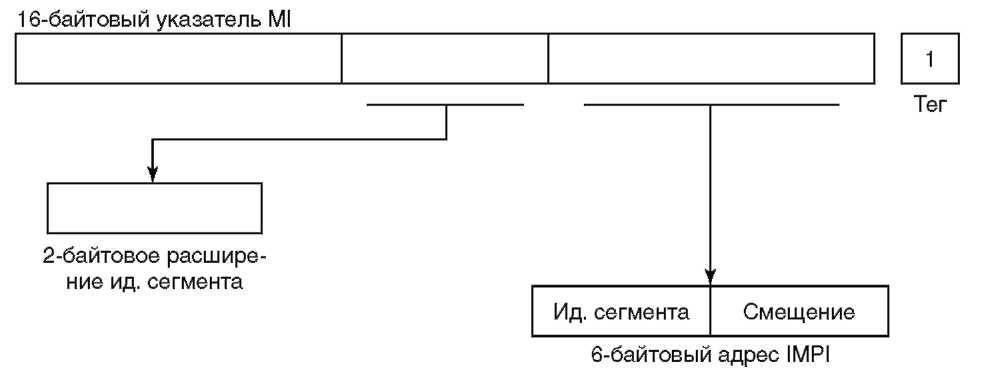

Указатель используется в AS/400 для доступа к объектам. В этом разделе мы сосредоточимся исключительно на формате разрешенного указателя. У разрешенного указателя две функции: он описывает объект и полномочия пользователя на этот объект; а также задает адрес объекта в одноуровневом хранилище. Иначе говоря, 16-байтовый указатель разделен на две 8-байтовые части: первая —описание объекта, а вторая — виртуальные адрес. В первой части разрешенного указателя находятся биты состояния, которые, кроме всего прочего, задают, что это за указатель: системный, пространственный, данных, команд или процедуры. В этой же части содержится информация об объекте и данных, доступных через этот указатель. Например, системный указатель задает для объекта тип системного объекта MI и подтип, определенный OS/400; а указатель данных описывает тип данных. Прочая информация первой части указателя касается полномочий пользователей на операции с объектом. Как отмечалось ранее, поле полномочий используется, только если указателем оперирует сама ОС в системном состоянии. В указателях, созданных пользовательскими программами в пользовательском режиме, поле полномочий не заполнено. Информация первой части указателя не занимает все 8, а лишь 4 байта. Это означает, что 4 байта указателя не используются. Они зарезервированы для будущих расширений адреса. Дополнительные 32 разряда вместе с 64 адресными разрядами указателя дают возможность расширить адрес AS/400 до 96 разрядов (12 байтов) без изменений каких-либо программ поверх MI. Если потребуется еще большее пространство, то можно будет удалить из указателя информацию типа и полномочий, и увеличить длину адреса сверх 96 разрядов. Вторая часть разрешенного указателя содержит 64-разрядный адрес. Так было всегда, и многие годы это вызывало путаницу: каков все же размер виртуального адреса System/38 и AS/400, 48- или 64-разрядный? С появлением новых RISC-моделей AS/400 путаница прекратилась: теперь адрес 64-разрядный. А в System/38 и ранних моделях AS/400 он был и таким, и таким. В MI адрес всегда был 64-разрядным, а аппаратура работала с 48-разрядным адресом. Как они уживались вместе — тема следующего раздела. Сказка о двух размерах адреса

Появление новых RISC-моделей с полностью 64-разрядными аппаратными адресами устранило большинство проблем, связанных со смешением 64- и 48-разрядной адресации в предыдущих моделях. Чтобы понять, почему 64-разрядный аппаратный адрес так важен, рассмотрим первоначальную 48-разрядную реализацию. 48-разрядный адрес появился в результате компромисса. Проектировщики ОС System/38 планировали адрес размером в 64 бита. После того, как размер указателя был определен в 16 байтов, для 64-разрядного адреса появилось достаточно места. Проблемы возникли на аппаратном уровне. Чем больше разрядов в адресе, тем больше размер регистров процессора. Больший размер регистров требовал большего числа цепей и повышал стоимость аппаратных средств.

Техническим менеджером System/38 был Рей Клотц, не видевший надобности в таком большом адресе. Его многократно пытались уговорить, но Рей так и не поддался на уверения, что 64-разрядного адреса хватит навечно. В середине 70-х годов подразделение IBM по мэйнфреймам собиралось объявить о новом большом адресе для System/370, получившем название расширенной адресации (XA). С применением ХА адрес System/370 должен был вырасти с 24 до 31 разряда. Рей обвинял нас в желании непременно превзойти System/370 и утешал тем, что 32 разряда все равно больше чем 31. «Вы побьете их и одним разрядом, а больше и не надо», — как бы говорил он. Мы, в свою очередь, утверждали, что 32-разрядный адрес не будет работать с одноуровневой памятью System/38, и что нужны 64 разряда. Когда стало очевидным, что спор зашел в тупик, мы поступили так, как будто торговались о цене подержанной машины: поделили пополам разницу между 32 и 64. Таким образом, получился 48-разрядный адрес. Для поддержки сегментированной памяти 48-разрядный адрес разделяется надвое. Старшие разряды задают сегмент, а младшие, называемые смещением — байт внутри сегмента. Мы решили использовать для задания сегмента старшие 32 разряда, а для смещения — младшие 16, назвав все это адресом 32/16. 16 разрядов смещения означали размер сегмента в 64 КБ (216 = 64 КБ). Оригинальная аппаратура процессора System/38 имела 16-разрядный тракт данных и 16-разрядный сумматор для вычислений. Смысл использования адреса форматом 32/16 был в том, чтобы смещение адреса не выходило за размер тракта данных, так как очень часто обновлялось. Мы решили обрабатывать 32-разрядный идентификатор сегмента не в тракте данных процессора, а вне его, в отдельном наборе сегментных регистров. К этим сегментным регистрам был возможен доступ со стороны процессора, но они не могли обновляться «на месте». Программисты, отвечавшие за ПО ОС ниже MI (первоначально VMC) не были согласны с такой адресацией (32/16), так как считали, что размер сегмента в 64 КБ слишком мал. Первоначально они предполагали создать сегментные группы, каждая из которых содержала бы один или несколько таких 64-килобайтных сегментов, но, в конце концов, решили, что сегментная группа всегда должна состоять из 256 сегментов. При выделении нового сегмента как части вновь создаваемого объекта его размер всегда будет равен 16 МБ (256 Г 64 КБ = 16 МБ). С этого момента мы говорили о 64-килобайтных и 16-мегабайтных сегментах, впрочем, называя иногда вторые сегментной группой. Этот разнобой в терминологии продолжался до появления процессоров PowerPC и SLIC. Если Вы возьмете в руки калькулятор или таблицу степеней двойки, то поймете, почему программисты VMC, имевшие дело с 16-мегабайтными сегментами, рассматривали 48-разрядный адрес как имеющий 24-разрядный идентификатор сегмента и 24-разрядное смещение (ведь 224 = 16 МБ). Представление адреса 24/24, использовавшееся VMC, не совпадало с представлением 32/16, использовавшимся аппаратурой. Возник вопрос: каким способом обрабатывать переполненное поле смещения адреса? Рассматривая объекты, мы говорили, что они состоят из одного или нескольких несмежных сегментов, и что ни один сегмент не может содержать части более чем одного объекта. Очевидно, что смещение адреса за границу сегмента в следующий сегмент нежелательно, так как последний может относиться к другому объекту. Следовательно, такое смещение, например, адреса в пространственном указателе за пределы ассоциированного пространства объекта, надо предотвратить. Определяется такое переполнение адреса следующим способом: после каждого увеличения адреса проверяется, не было ли переноса из разрядов смещения в разряды идентификатора сегмента. Такой перенос и означает попытку обратиться к следующему сегменту. Подобные ошибки переполнения могут легко отслеживаться аппаратно, для чего используется механизм прерываний[ 66 ]. Прерывания будут рассмотрены в главе 9, но одно из них мы обсудим прямо сейчас: переполнение эффективного адреса (ЕАО). Разберем ситуацию, возникавшую в System/38 при переполнении 16-разрядного смещения. В этом случае аппаратура не увеличивала 32-разрядную сегментную часть адреса. Вместо этого об исключительной ситуации сообщалось VMC, который в каждом конкретном случае заново оценивал ситуацию. VMC рассматривал сегменты, как имеющие длину 16 МБ и состоящие из 256 аппаратных сегментов меньшего размера, и поэтому переполнение 64-килобайтного сегмента в середине 16-мегабайтного сегмента переполнением не считал. С его точки зрения — представления адреса 24/ 24 — переполнением считался только перенос из младших 24 разрядов в старшие 24. При каждом прерывании по ЕАО VMC увеличивал 32-разрядный аппаратный идентификатор сегмента, проверял, нет ли переноса в старшие 24 разряда, и если обнаруживал, что все в порядке, управление возвращалось аппаратуре. Таким образом, мы постоянно сталкивались с несовпадением схем 32/16 и 24/24. Когда с течением времени ширина тракта данных процессора выросла с первоначальных 16 до 32, а затем до 48 разрядов, разделение регистров сегмента и смещения в аппаратуре стали менее важны. В IMPI-моделях AS/400 были добавлены команды для поддержки адреса 24/24, что исключило необходимость программной обработки переполнений. Однако в целях совместимости с оригинальным VMC, представление 32/ 16 было в IMPI сохранено. Эта проблема с адресами была не единственной в оригинальном VMC. Он должен был поддерживать 64-разрядный адрес в указателе MI на аппаратуре с 48-разрядным адресом. Можно было бы попытаться рассматривать 64-разрядные адреса как виртуальные адреса большего размера, которые каким-то образом отображаются в меньшие 48-разрядные виртуальные адреса, но такое решение было отвергнуто. Вместо этого, старшие 16 разрядов 64-разрядного адреса стали рассматриваться как отдельное значение. Мы назвали это 16-разрядное поле расширением идентификатора сегмента, обозначив его номером IPL. При всякой перезагрузке системы номер IPL увеличивался на единицу, что каждый раз давало новое 48-разрядное адресное пространство. На рисунке 8.2 показаны поля, составляющие 64-разрядный адрес в указателе MI.

Рисунок 8.2. Оригинальный формат адреса указателя MI Первоначально заголовок сегмента, описанный в главе 5, содержал поле с 16-разрядным расширением идентификатора этого сегмента. Когда программа MI пыталась использовать указатель на System/38 и на ранних моделях AS/400, для проверки битов тега и загрузки 48-разрядного адреса в процессорный регистр, использовалась специальная команда IMPI под названием «Загрузить и проверить теги» («lvt»). Команда «lvt» аналогична «lq» на RISC-процессорах, но у первой была дополнительная задача. Она должна была сравнить старшие 16 разрядов адреса в указателе с полем расширения идентификатора в заголовке сегмента и гарантировать их совпадение с адресом сегмента. После первого обращения для доступа к сегменту использовался только 48-разрядный адрес. Как уже говорилось, всякий раз при увеличении номера IPL мы получали новое адресное пространство для временных объектов. Временные объекты разрушаются при выполнении IPL, в отличие от постоянных, продолжающих существовать и после перезагрузки. Так как аппаратура использовала только 48 разрядов, один и тот же 48-разрядный адрес не мог быть задействован для постоянных объектов повторно, за исключением случая, когда постоянный объект по этому адресу был явно удален во время предыдущего сеанса работы ОС. Тогда от него оставались только заголовки, что обнаруживалось при первом использовании полного 64-разрядного адреса, начальные 16 разрядов которого содержат номер IPL. Так как номера IPL различались, то при повторном использовании 48-разрядного адреса конфликтов не возникало. Еще раз подчеркну, что заголовки сохраняются только при разрушении постоянных объектов — при разрушении временного объекта не остается ничего.