|

||||

|

|

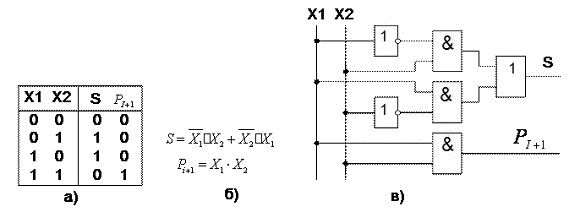

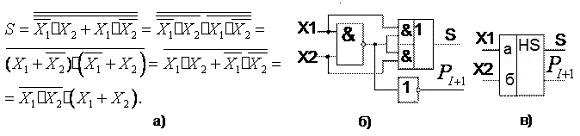

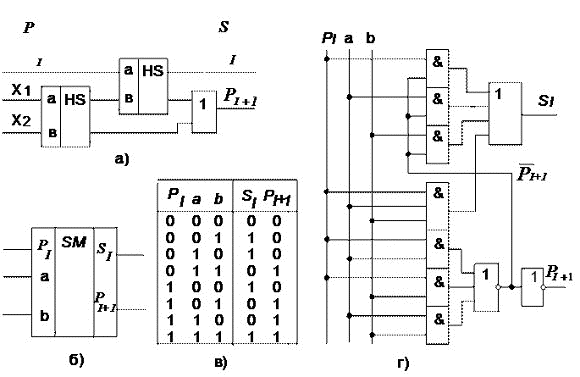

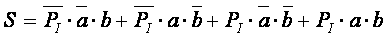

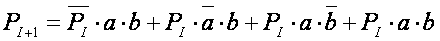

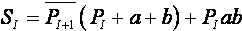

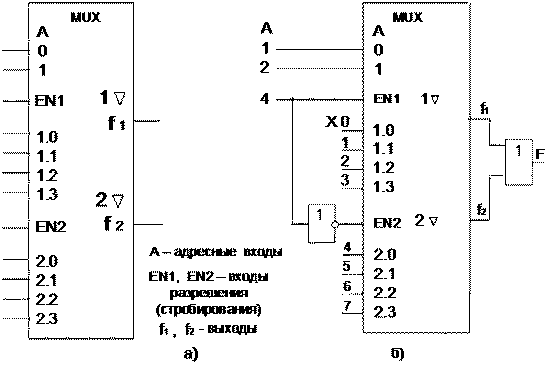

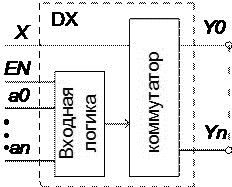

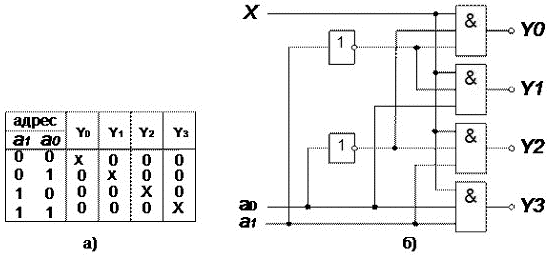

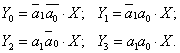

4 Цифровые устройства комбинационного типа Цифровыми устройствами комбинационного типа или цифровыми автоматами без памяти называются цифровые устройства, логические значения на выходе которых однозначно определяются совокупностью или комбинацией сигналов на входах в данный момент времени. К ним относятся суммирующие схемы, шифраторы и дешифраторы, мультиплексоры и демультиплексоры, цифровые компараторы и другие устройства. Цифровые устройства комбинационного типа выпускаются в виде интегральных микросхем или входят в состав больших интегральных микросхем, таких как процессоры, запоминающие и другие устройства. 4.1 Двоичные сумматоры 4.1.1 Одноразрядные сумматоры В цифровой вычислительной технике используются одноразрядные суммирующие схемы с двумя и тремя входами, причём первые называются полусумматорами, а вторые — полными одноразрядными сумматорами. Полусумматоры могут использоваться только для суммирования младших разрядов чисел. Полные одноразрядные сумматоры имеют дополнительный третий вход, на который подаётся перенос из предыдущего разряда при суммировании многоразрядных чисел. На рисунке 21, а) приведена таблица истинности полусумматора, на основании которой составлена его структурная формула в виде СДНФ (Рисунок 21, б). Функциональная схема, составленная на элементах основного базиса в соответствии с этой структурной формулой, приведена на рисунке 21, в).  Рисунок 21 Одноразрядный полусумматор: а) таблица истинности, б) структурная формула, в) функциональная схема. Основными параметрами, характеризующими качественные показатели логических схем, являются быстродействие и количество элементов, определяющее сложность схемы. Быстродействие определяется суммарным временем задержки сигнала при прохождении элементов схемы. В приведённой выше схеме быстродействие определяется задержкой в трёх логических элементах. Кроме количества элементов сложность схемы, как было отмечено выше, определяется количеством входов элементов, по которым выполняются логические операции. Этот параметр называется «Число по Квайну». Приведённая выше схема содержит 6 элементов и имеет 10 входов (Число по Квайну равно 10). Недостатком схемы рисунок 21, в) является то, что на её входы необходимо подавать и прямые и инверсные значения операндов. Применяя законы алгебры логики схему можно преобразовать, исключив инверсии над отдельными операндами. Порядок минимизации показан на рисунке 22, а), функциональная схема — на рисунке 22, б), а её УГО — на рисунке 22, в).  Рисунок 22 Пример минимизации а), функциональная схема б) и УГО одноразрядного полусумматора в). Минимизированная схема является более быстродействующей, так как вместо 6 содержит 3 элемента, а число по Квайну уменьшилось с 10 до 7. Учитывая огромное количество используемых суммирующих схем, выигрыш можно считать весьма ощутимым. Схему полного одноразрядного сумматора можно получить на основе двух схем полусумматоров и схемы «ИЛИ», как показано на рисунке 23,а).  Рисунок 23 Одноразрядный полный сумматор: а) — функциональная схема на двух полусумматорах; б) — УГО; в) — таблица истинности: г) — минимизированная схема. Из рассмотрения принципа работы функциональной схемы рисунок 23,а) составлена её таблица истинности, анализ которой показывает, что данная схема выполняет функции полного одноразрядного сумматора. Однако схема не является оптимальной по быстродействию, поскольку в ней сигнал проходит последовательно через две схемы полусумматоров и схему ИЛИ. Представляется целесообразным разработка сумматора как устройства, имеющего три входа и два выхода. СДНФ такой функции записывается в виде:   Минимизированные значения, используемые в интегральной схемотехнике:  PI+1 = PIa + PIb + ab Первое из уравнений минимизируется аналитическим методом, используя законы алгебры логики, а второе — методом минимизирующих карт Карно. Функциональная схема, составленная по этим уравнениям, приведена на рисунке 23, г). По сравнению со схемой рисунок 23, а) эта схема является более быстродействующей. Условное графическое обозначение (УГО) схемы полного одноразрядного сумматора приведено на рисунке 23, б). 4.1.2 Многоразрядные сумматоры Методы построения многоразрядных сумматоров: - Последовательное суммирование; - Параллельное суммирование с последовательным переносом; - Параллельное суммирование с параллельным переносом.  Рисунок 24 Суммирование многоразрядных чисел: а) — Последовательное; б) — Параллельное с последовательным переносом При последовательном суммировании используется один сумматор, общий для всех разрядов (Рисунок 24, а). Операнды должны вводиться в сумматор через входы аI и bI синхронно, начиная с младших разрядов. Цепь задержки обеспечивает хранение импульса переноса PI+1 на время одного такта, то есть до прихода пары слагаемых следующего разряда, с которыми он будет просуммирован. Задержку выполняет D-триггер. Результаты суммирования также считываются последовательно, начиная с младших разрядов. Для хранения и ввода операндов на входы сумматора, а также для записи результата суммирования обычно используются регистры сдвига. Достоинство этого метода — малые аппаратные затраты. Недостаток — невысокое быстродействие, так как одновременно суммируются только пара слагаемых. Схема параллельного сумматора с последовательным переносом приведена на рисунке 24, б). Количество сумматоров равно числу разрядов чисел. Выход переноса PI+1 каждого сумматора соединяется со входом переноса PI следующего более старшего разряда. На входе переноса младшего разряда устанавливается потенциал «0», так как сигнал переноса сюда не поступает. Слагаемые aI и bI суммируются во всех разрядах одновременно, а перенос PI поступает с окончанием операции сложения в предыдущем разряде. Быстродействие таких сумматоров ограничено задержкой переноса, так как формирование переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал переноса не распространится по всей цепочке сумматоров. Параллельные сумматоры с параллельным переносомДля организации параллельного переноса применяются специальные узлы — блоки ускоренного переноса. Принцип ускоренного переноса заключается в том, что для каждого двоичного разряда дополнительно находятся два сигнала: G — образование переноса и H — распространение переноса. GI = aI·bI HI = aI + bI В случае GI=1, то есть aI=bI=1, в данном i-разряде формируется сигнал переноса PI+1 в следующий высший разряд независимо от формирования функций суммы в предыдущих разрядах. Если хотя бы одно из слагаемых aI или bI равно «1», то есть HI=1, то перенос в последующий разряд производится при наличии сигнала переноса из предыдущего разряда. Если HI=HI–1=1 и при этом существует сигнал переноса PI из предыдущего в i-й разряд, то перенос производится сразу в i+2 разряд. В общем случае процесс формирования ускоренного переноса описывается следующим уравнением: PI+1 = GI + HI·GI–1 + HI·HI–1·GI–2 + … + HI·HI–1·…·H2·H1·P1 Блоки ускоренного переноса выпускаются в интегральном исполнении в виде отдельных микросхем или непосредственно со схемой сумматора или арифметико-логического устройства в одной микросхеме. 4.1.3 Арифметико-логические устройства Основными арифметическими операциями являются сложение и вычитание. Разработаны коды дополнительный и обратный, которые позволяют выполнять операцию вычитания методом суммирования. Для выполнения операции вычитания, при использовании дополнительного кода, вычитаемое следует перевести в дополнительный код и просуммировать с первым слагаемым. Полученный результат (разность) будет представлен в дополнительном коде. Затем его следует перевести в прямой код.

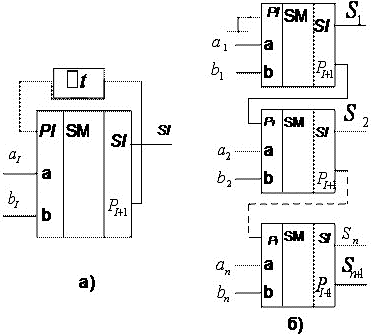

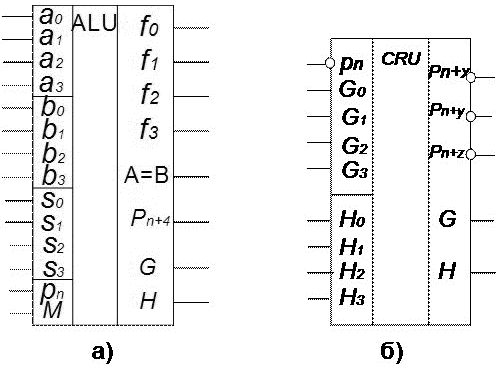

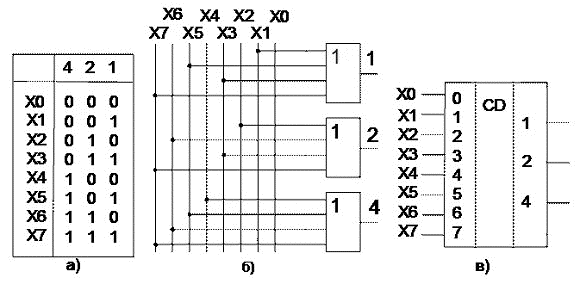

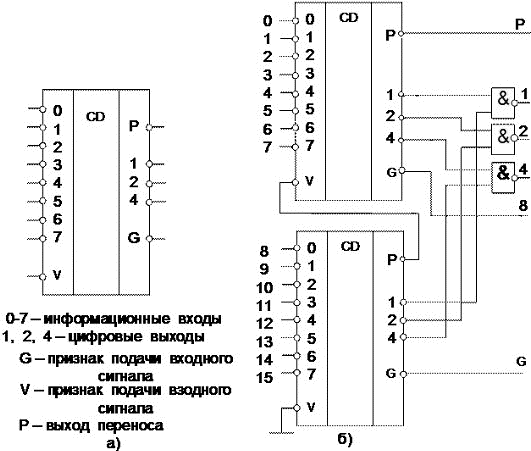

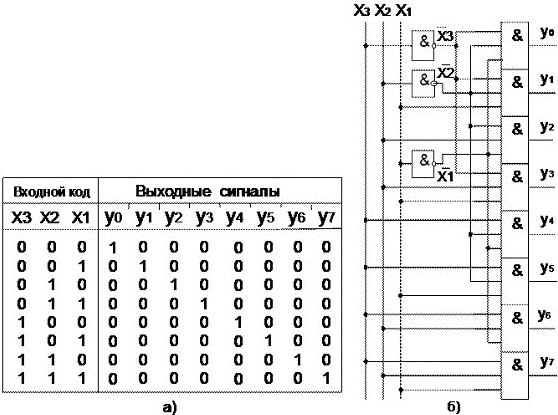

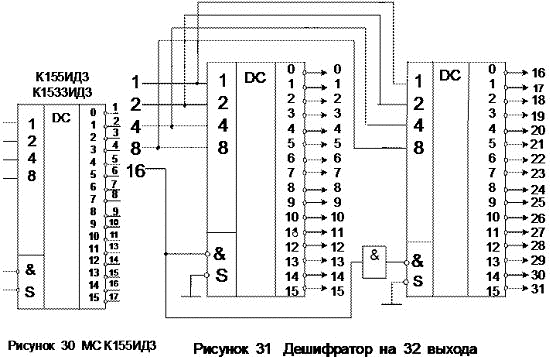

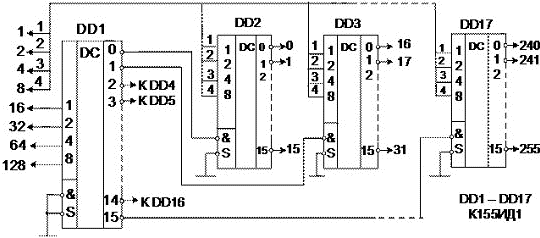

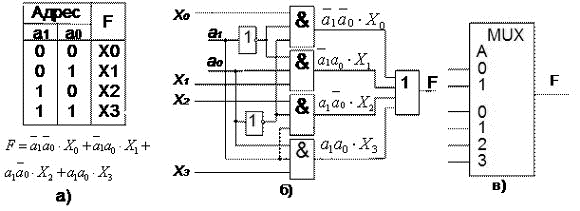

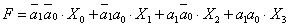

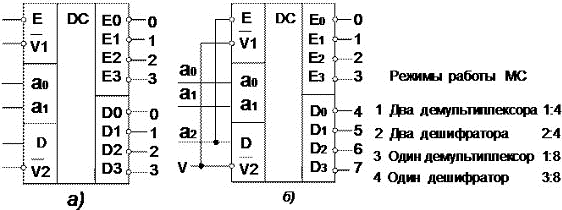

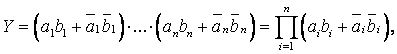

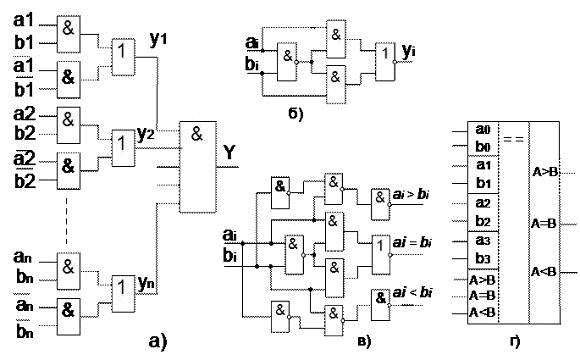

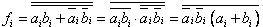

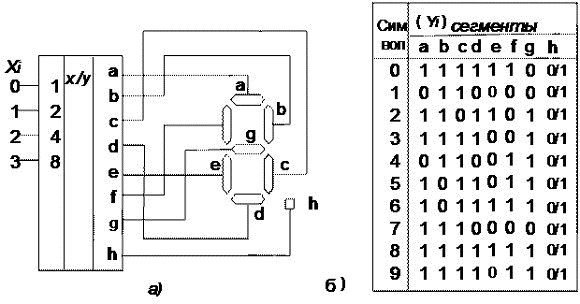

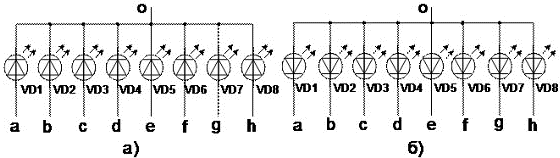

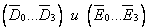

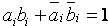

Таким образом, выполнение операции вычитания методом суммирования требует дополнительных затрат времени и снижает быстродействие вычислительных средств. Для повышения быстродействия ЭВМ разработаны и используются комбинированные арифметико-логические устройства, которые обеспечивают выполнение ряда арифметических и логических операций над прямыми кодами чисел без их преобразования. Методика построения одноразрядного арифметического устройства для выполнения операций суммирования и вычитания показана на рисунке 25. Из сравнения логических выражений операций суммирования (Рисунок 25, а) и вычитания (Рисунок 25, б) следует, что выражения для суммы и разности совпадают, а выражение для заёма является частью операции суммирования или вычитания.  Рисунок 25 Таблицы истинности и структурные формулы операции суммирования а), вычитания б) и схема одноразрядного АЛУ в). Таким образом, для выполнения операции вычитания не требуется получение дополнительных сигналов, поэтому и не требуются дополнительные аппаратные затраты. Необходимо лишь обеспечить коммутацию сигналов переноса и заёма в соответствии с кодом операции. На рисунке 25, в) приведена схема простейшего АЛУ, на которой роль устройства управления выполняют два клапана, управляемые разнополярными сигналами от управляющего напряжения U. Эта часть схемы на рисунке 25,в выделена пунктирной линией. При U=0 выполняется операция вычитания, а при U=1 — операция суммирования. Многоразрядные АЛУ выпускаются в виде интегральных микросхем или входят в состав процессоров, являясь их основой. МС 564ИП3 (Рисунок 26,а) — это 4-разрядное параллельное АЛУ, выполняющая 16 арифметических и 16 логических операций.  Рисунок 26 Схема 4-разрядного АЛУ 564ИП3 а) и схема ускоренного переноса 564ИП4 б). A(а0–а3) — первый операнд, B(b0–b3) — второй операнд, S(s0–s3) — код операции — 4 разряда. Если M=0, то выполняются арифметические операции: 24=16, при M=1 выполняются логические операции: 24=16. Итого 16+16=32 операции. F(f0–f3) — результат операции. На выходе A=B появляется «1», если при выполнении операции вычитания результат операции будет равен «0», то есть A=B. Поскольку АЛУ параллельного типа, то имеются выходы генерации G и распространения переноса H. Pn и Рn+4 — входной и выходной переносы. Для увеличения разрядности обрабатываемых слов МС АЛУ можно соединять последовательно, как и в параллельных сумматорах с последовательным переносом. При этом, конечно, увеличивается время выполнения операций. Уменьшить это время и, следовательно, увеличить быстродействие АЛУ можно применением схемы ускоренного переноса 564ИП4, рисунок 26, б). Используя четыре МС АЛУ и одну МС ускоренного переноса можно получить 16-разрядное полностью параллельное АЛУ, время суммирования которого равно времени суммирования одной микросхемы. 4.2 Кодирующие и декодирующие устройства 4.2.1 Шифраторы Шифратор (кодер) — это функциональный узел, предназначенный для преобразования поступающих на его входы управляющих сигналов (команд) в n-разрядный двоичный код. В частности, такими сигналами или командами могут быть десятичные числа, например, номер команды, который с помощью шифратора преобразуется в двоичный код. В качестве примера разработаем схему 3-разрядного шифратора. Вначале следует построить таблицу кодов (таблицу истинности), в которой код номера сигнала представим, например, двоичным кодом (Рисунок 27,а). Схема, реализованная на элементах ИЛИ, приведена на рисунке 27,б.  Рисунок 27 Таблица кодов 3-разрядного шифратора а), его функциональная схема б) и УГО в). В общем случае, при использовании двоичного кода, можно закодировать 2n входных сигналов. В рассмотренной выше схеме выходной код «000» будет присутствовать на выходе при подаче сигнала на вход X0 и в случае, если входной сигнал вообще не подаётся ни на один из входов. Для однозначной идентификации сигнала X0 в интегральных схемах формируется ещё один выходной сигнал — признак подачи входного сигнала, который используется и для других целей. На рисунке 28 приведено УГО схемы 3-х разрядного приоритетного шифратора на 8 входов.  Рисунок 28 3-разрядный приоритетный шифратор К555ИВ1 а) и соединение двух МС б) При подаче сигнала на любой из входов, устанавливается G=1, P=0, а на цифровых выходах — двоичный код номера входа, на который подан входной сигнал. Если сигнал подан одновременно на два или несколько входов, то на выходе установится код входа с большим номером. Отсюда название шифратора «приоритетный». Если сигнал (лог.«0») подан на один из входов 0…7, то на выходах DD3 появятся младшие разряды прямого кода, на выходе G DD1 — лог. «0», определяющий разряд с весовым коэффициентом 8 выходного кода, на выходе P — лог. «1». Если лог.«0» подан на один из входов 8…15, то сигнал лог. «1» с выхода P DD2 запретит работу DD1. При этом младшие разряды на выходах DD3 определяются уже микросхемой DD2, а на выходе 8 выходного кода будет лог. «1». Таким образом, с выходов 1, 2, 4, 8 можно снять прямой код, соответствующий номеру входа, на который подан входной сигнал. 4.2.2 Дешифраторы (декодеры) Дешифратор — функциональный узел, вырабатывающий сигнал «лог. 1» (дешифратор высокого уровня) или сигнал «лог. 0» (дешифратор низкого уровня) только на одном из своих 2n выходах в зависимости от кода двоичного числа на n входах.  Рисунок 29 Дешифратор: а) – таблица истинности; б) – функциональная схема Дешифраторы широко используются в устройствах управления, где они формируют управляющий сигнал в соответствии с входным кодом, который воздействует на какое-либо исполнительное устройство. Интегральные микросхемы дешифраторов изготавливаются с дополнительными входами, например, с входом разрешения (стробирования). Стробирование позволяет исключить появление на входах дешифратора ложных сигналов, запрещая его работу в интервале времени переходного процесса при изменении цифрового кода на входе. Микросхема ИД3 (рисунок 30) имеет четыре адресных входа с весовыми коэффициентами двоичного кода 1, 2, 4, 8, два инверсных входа стробирования S, объединённых по И, и 16 инверсных выходов 0–15. Если на обоих входах стробирования «лог. 0», то на том из выходов, номер которого соответствует десятичному эквиваленту входного кода, будет «лог. 0». Если хотя бы на одном из входов стробирования S «лог. 1», то независимо от состояния входов на всех выходах микросхемы формируется «лог. 1».  Наличие двух входов стробирования существенно расширяет возможности использования микросхем. Из двух микросхем ИД3, дополненных одним инвертором, можно собрать дешифратор на 32 выхода (рисунок 31), а из 17 микросхем — дешифратор на 256 выходов (рисунок 32).  Рисунок 32 Дешифратор на 256 выходов 4.3 Коммутаторы цифровых сигналов 4.3.1 Мультиплексоры Мультиплексор — функциональный узел, который имеет n адресных входов, N=2n информационных входов, один выход и осуществляет управляемую коммутацию информации, поступающей по N входным линиям, на одну выходную линию. Коммутация определённой входной линии происходит в соответствии с двоичным адресным кодом an-1,…a2,a1,a0. Если адресный код имеет n разрядов, то можно осуществить N=2n комбинаций адресных сигналов, каждая из которых обеспечит подключение одной из N входных линий к выходной линии. Такой мультиплексор называют «из N в одну». При наличии избыточных комбинаций адресных сигналов можно спроектировать мультиплексор с любым числом входных линий N≤2n. В простейшем случае при двухразрядном адресном коде (n=2) максимальное число входных адресных линий равно N=2n=4. Таблица истинности такого мультиплексора приведена на рисунке 33,а.  Рисунок 33 Мультиплексор 4:1 а) — Таблица истинности; б) — Функциональная схема; в) — Условное графическое обозначение. Характеристическое уравнение такого мультиплексора, записанное в соответствии с таблицей истинности, имеет вид:  Из полученного уравнения следует, что в состав функциональной схемы мультиплексора входят два инвертора, четыре схемы «И» и одна схема «ИЛИ» (Рисунок 33,б). Здесь адресными (управляющими) входами являются а1, а0, а информационными — Х0, Х1, Х2, Х3. Условное графическое обозначение мультиплексора, в соответствии с ГОСТ 2.743-91, приведено на рисунке 33,в. В настоящее время промышленность выпускает МС, в серии которых входят мультиплексоры с n=2, 3 и 4 адресными входами. При n=2 выпускаются сдвоенные четырёхканальные (2n=4) мультиплексоры, число входных информационных сигналов которых равно 2n+2n=8. УГО сдвоенного 4-канального мультиплексора со стробированием К555КП12 приведено на рисунке 34,а.  Рисунок 34 Сдвоенный 4-канальный мультиплексор К555КП12 а) и 8-канальный мультиплексор на его основе б). Входы стробирования используются для построения мультиплексоров (коммутаторов) с k2n-информационными входами, k=2, 3, 4… Схема мультиплексора 8:1 на основе сдвоенного 4-канального мультиплексора со стробированием приведена на рисунке 34,б. Если подавать на информационные входы Xi постоянные уровни, соответствующие лог. «0» или лог. «1», то на выходе мультиплексора можно получить любую желаемую функцию переменных управляющего кода. При этом число переменных в реализуемой выходной функции будет равно разрядности управляющего кода. В общем случае на информационные входы можно подавать не постоянные логические уровни, тогда на выходе мультиплексора реализуется логическая функция с большим числом переменных. 4.3.2 Дешифраторы-демультиплексоры Демультиплексор — это функциональный узел, осуществляющий управляемую коммутацию информацию, поступающую по одному входу, на N выходов. Таким образом, демультиплексор реализует операцию, противоположную той, которую выполняет мультиплексор. Обобщённая схема демультиплексора приведена на рисунке 35. В общем случае число выходных линий N определяется количеством адресных входов n и равно N=2n. Для случая n=2 функционирование демультиплексора осуществляется в соответствии с таблицей истинности, приведённой на рисунке 36,а.  Рисунок 35 Обобщённая схема демультиплексора  Рисунок 36 Таблица истинности — а) и функциональная схема 4-канального демультиплексора — б) Из таблицы истинности записываем характеристические уравнения демультиплексора:  Соответствующая этим уравнениям функциональная схема демультиплексора приведена на рисунке 36,б. Она имеет в своём составе два инвертора и четыре элемента «И». Сравнивая таблицы истинности и функциональные схемы демультиплексора и дешифратора, легко увидеть схожесть их функций. Если функция X=1 постоянно, то демультиплексор выполняет функции дешифратора. Учитывая схожесть выполняемых функций, микросхемы дешифраторов и демультиплексоров имеют одинаковое условное обозначение — ИЕ, называются «Дешифратор-демультиплексор» и могут выполнять функции и дешифратора и демультиплексора. В качестве примера рассмотрим микросхему К155ИД4, УГО которой приведено на рисунке 37,а. Это сдвоенный 4-канальный дешифратор-демультиплексор. Каждая секция имеет один информационный вход (D и Ē), один вход разрешения  Рисунок 37 Микросхема К155ИД4 а) и возможные режимы её работы б). Наличие у МС прямого и инверсного информационных входов позволяет простым их объединением получить третий адресный разряд а2, а двух инверсных входов разрешения — общий вход разрешения дешифратора 3:8 или информационный вход демультиплексора 1:8. Рассмотренную выше микросхему дешифратора К155ИД3 можно использовать в качестве демультиплексора с форматом 1:16. При этом входы разрешения дешифрации используются в качестве основного информационного входа X, а адресные входы и выходы используются по прямому назначению. 4.4 Устройства сравнения кодов. Цифровые компараторы Устройства сравнения кодов предназначены для выработки выходного сигнала в случае, когда поступающие на их входы коды двух чисел оказываются одинаковыми. Числа A и B считаются равными, если разрядные коэффициенты чисел A и B оказываются одинаковыми, то есть, если ai=bi=1 или ai=bi=0. Эти равенства можно привести к одному:  где n — число разрядов.  Рисунок 38 Устройства сравнения кодов: а) — структурная схема; б) — минимизированный вариант схемы сравнения в одном разряде; в) — одноразрядный компаратор; г) — УГО 4-разрядного компаратора. Структурная схема устройства сравнения кодов, составленная на основании приведённого выше уравнения приведена на рисунке 38,а. Выходной сигнал Y=1 будет иметь место только при условии, если будут единичными результаты сравнения во всех разрядах сравниваемых чисел. Недостатком рассмотренной схемы является большое число входов, так как для работы устройства требуются не только прямые, но и инверсные коды чисел A и В. На основе законов алгебры логики разработаны устройства сравнения, работающие только с прямыми кодами.  Схема одноразрядного элемента сравнения, построенная на основании этого уравнения, приведена на рисунке 38,б. Функциональная схема, построенная на этих элементах, будет иметь вдвое меньшее число входов. Цифровые компараторы являются универсальными элементами сравнения, которые помимо констатации равенства двух чисел, могут установить какое из них больше. Простейшая задача состоит в сравнении двух одноразрядных чисел. Схема одноразрядного компаратора приведена на рисунке 38,в. При рассмотрении принципа работы схемы следует иметь в виду, что если ai < bi, то ai = 0, а bi = 1 и наоборот. Для сравнения многоразрядных чисел используется следующий алгоритм. Сначала сравниваются значения старших разрядов. Если они различны, то эти разряды и определяют результат сравнения. Если они равны, то необходимо сравнивать следующие за ними младшие разряды, и т. д. Цифровые компараторы выпускают в виде отдельных микросхем. Например, К561ИП2 позволяет сравнивать два 4-разрядных числа с определением знака неравенства. УГО этой МС приведено на рисунке 38,г. Устройство обладает свойством наращиваемости разрядности сравниваемых чисел. Для сравнения, например, 8-разрядных чисел можно применить две четырёхразрядные микросхемы. Для этой цели в МС К561ИП2 предусмотрены три дополнительных входа: A > B, A = B и A > B, к которым подводятся соответствующие выходы микросхемы, выполняющей сравнение младших разрядов. Если используется только одна микросхема, то на вход A = B надо подать лог. «1», а на входы A < B и A > B — дог. «0». 4.5 Преобразователи кодов. Индикаторы Операция изменения кода числа называется его преобразованием. Интегральные микросхемы, выполняющие эти операции, называются преобразователями кодов. Интегральные микросхемы преобразователей кодов выпускаются только для наиболее распространённых операций таких как преобразователи двоичного кода в десятичный, двоично-десятичный, шестнадцатеричный, код Грея или обратных, указанным выше, преобразований. По своей структуре преобразователи кодов являются дешифраторами, только они преобразуют двоичный код в сигналы не только на одном, но и на нескольких выходах. В качестве примера рассмотрим преобразователь двоичного кода в код управления 7-сегментным цифровым индикатором. На рисунке 39,а приведена схема подключения индикатора. Индикатор представляет собой полупроводниковый прибор, в котором имеется восемь сегментов, выполненных из светодиодов. Включением и выключением отдельных сегментов можно получить светящееся изображение отдельных цифр или знаков. Конфигурация и расположение сегментов индикатора показаны на рисунке 39,а. Каждой цифре соответствует свой набор включения определённых сегментов индикатора. Соответствующая таблица отображения цифр и десятичной разделительной точки приведена на рисунке 39,б.  Рисунок 39 Преобразователь двоичного кода в код 7 – сегментного индикатора: а) — Схема подключения индикатора; б) — Таблица состояний. По внутренней схеме включения индикаторы подразделяются на индикаторы с общим катодом и с общим анодом. Схемы обоих видов индикаторов приведены на рисунке 40,а и 40,б соответственно. Существует широкая гамма различных модификаций семисегментных индикаторов. Они отличаются друг от друга размерами, цветом свечения, яркостью, расположением выводов.  Рисунок 40 Схемы индикаторов: а) — с общим катодом; б) — с общим анодом. Для управления индикатором с общим катодом используется, например, дешифратор К514ИД1, а с общим катодом — К514ИД2. Используются микросхемы дешифраторов и других серий, например, 176ИД2, 176ИД3, 564ИД4, 564ИД5, К133ПП1 и др. Шкальные индикаторы (светящиеся столбики) представляют собой линейку светодиодов с одним общим анодом или катодом. Они являются аналогами щитовых измерительных приборов и служат для отображения непрерывно изменяющейся информации. Светящиеся шкалы могут быть установлены на приборном щитке автомобиля или самолёта для индикации уровня горючего в баке, скорости движения и других параметров. Удобна конструкция в виде расположенных рядом столбиков для индикации величин с целью их сравнения. Преобразователи двоичного кода в код управления шкальным индикатором обеспечивают перемещение светящегося пятна, определяемое двоичным кодом на адресном входе. Матричные индикаторы представляют собой наборы светодиодов, расположенных по строкам и столбцам. Наиболее распространённые матричные индикаторы имеют 5 столбцов и 7 строк (формат 5×7). Количество светодиодов таких индикаторов равно 35. Для управления матричными индикаторами выпускаются микросхемы, в которых положение светодиода задаётся номерами строки и столбца, причём не все комбинации используются. Такие преобразователи кодов называются неполными. К ним относятся, например, микросхемы К155ИД8 и К155ИД9. |

|

||

|

Главная | Контакты | Нашёл ошибку | Прислать материал | Добавить в избранное |

||||

|

|

||||

, четыре выхода

, четыре выхода  и два общих адресных входа (a1, a0). Возможные способы включения и режимы работы показаны на рисунке 36,б.

и два общих адресных входа (a1, a0). Возможные способы включения и режимы работы показаны на рисунке 36,б. . Поскольку это равенство выполняется для каждого разряда, то выходной сигнал Y можно представить в виде логической функции:

. Поскольку это равенство выполняется для каждого разряда, то выходной сигнал Y можно представить в виде логической функции: