|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

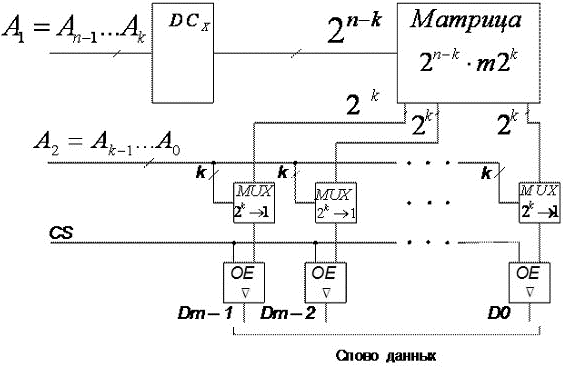

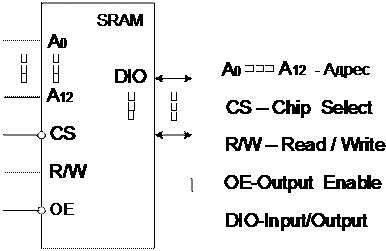

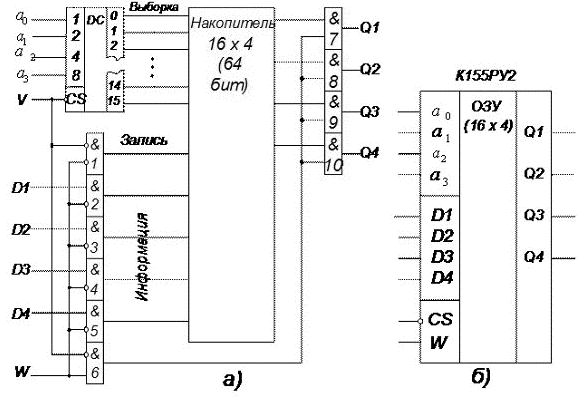

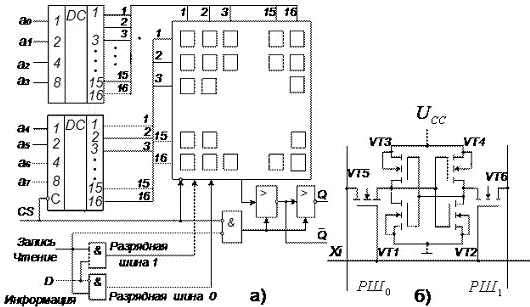

6 Запоминающие устройства 6.1 Иерархия запоминающих устройств ЭВМ Запоминающие устройства (ЗУ) служат для хранения информации и обмена ею с другими устройствами. Микросхемы и системы памяти постоянно совершенствуются как в области схемотехнологии, так и в области развития новых архитектур. Важнейшие параметры ЗУ находятся в противоречии. Так, например, большая информационная ёмкость не сочетается с высоким быстродействием, а быстродействие в свою очередь не сочетается с низкой стоимостью. Поэтому в ЗУ используется многоступенчатая иерархическая структура. В наиболее развитой иерархии памяти ЭВМ можно выделить следующие уровни. Регистровые ЗУ — находятся внутри процессора. Благодаря им уменьшается число обращений к другим уровням памяти, находящимся вне процессора и требующим большего времени для операции обмена. Кэш-память — быстродействующая память, которая может находиться внутри или вне процессора. Она предназначена для хранения копий информации, находящейся в более медленной основной памяти. Оперативная память (RAM — Read Access Memory) или оперативное запоминающее устройство (ОЗУ) — часть основной памяти ЭВМ, предназначенной для хранения быстро изменяемой информации. В ОЗУ хранятся программы пользователей промежуточные результаты вычислений. Постоянная память (ROM — Read Only Memory — память только для чтения) или постоянное запоминающее устройство (ПЗУ) — это вторая часть основной памяти ЭВМ, предназначенной для хранения редко меняемой информации, например, кодов команд, тестовых программ. Специализированные виды памяти, например, видеопамять, предназначенная для хранения информации, отображаемой на экране дисплея и др. Внешняя память — магнитные и оптические диски, FLASH-память, предназначенные для хранения больших объёмов информации. 6.2 Структурные схемы ЗУ ЗУ адресного типа состоят из трёх основных блоков: - Массив элементов памяти, - Блок адресной выборки, - Блок управления. Многочисленные варианты ЗУ имеют много общего с точки зрения структурных схем. Общность структур особенно проявляется для статических ОЗУ и памяти ROM; для них характерны структуры 2D, 3D и 2DM. Структура 2DВ ЗУ, с информационной ёмкостью M, запоминающие элементы организованы в матрицу размерностью k·m: M = k·m, где k — количество хранимых слов, m — их разрядность. Дешифратор адресного кода имеет k выходов и активизирует одну из выходных линий, разрешая одновременный доступ ко всем элементам выбранной строки, хранящей слово. Элементы каждого из столбцов соединены вертикальными разрядными линиями и хранят одноимённые биты всех слов. Таким образом, при наличии разрешающего сигнала CS, выбранная дешифратором ячейка памяти подключается к разрядным шинам, по которым производится запись или считывание адресованного слова. Структура 3DСтруктура типа 2D применяется лишь в ЗУ с малой информационной ёмкостью, т.к. при росте ёмкости усложняется дешифратор адреса. Например, при коде разрядностью n=8 дешифратор должен иметь 2n=256 выходов. В структуре типа 3D выборка элемента памяти из массива производится по двум координатам. Код адреса разрядностью n делится на две половины и используются два дешифратора: по строкам и по столбцам. При этом число выходов двух дешифраторов равно 2n/2+2n/2=2n/2+1. Если n=8, то число выходов дешифраторов равно 24+24=32, а количество элементов памяти равно 2n/2·2n/2=2n=256. В структуре 2D-типа, как уже было отмечено выше, потребовался бы более сложный дешифратор на 256 выходов. Таким образом, с помощью двух дешифраторов, имеющих небольшое число выходов, осуществляется доступ ко всем элементам памяти микросхемы. Структура 3D может применяться и в ЗУ с многоразрядной организацией, принимая при этом «трёхмерный» характер. В этом случае несколько матриц управляются от двух дешифраторов, относительно которых матрицы включены параллельно. Структура 2DM (Рисунок 67)состоит из дешифратора, который выбирает целую строку. Однако, в отличие от структуры 2D, длина строки многократно превышает разрядность хранимых слов. При этом число строк уменьшается и, следовательно, уменьшается число выводов дешифратора. Выбор строк матрицы памяти производится с помощью старших разрядов адреса An-1…Ak. Остальные k разрядов используются для выбора необходимого m-разрядного слова из множества слов, содержащихся в строке.  Рисунок 66 Структура ЗУ типа 2DM для ROM Это выполняется с помощью мультиплексоров, на адресные входы которых подаются коды Ak-1…A0. Длина строки равна m·2k, где m — разрядность слов. Из каждого отрезка строки, длиной 2k, мультиплексор выбирает один бит. На выходах m мультиплексоров формируется выходное m-разрядное слово. По разрешению сигнала CS, поступающего на входы OE управляемых буферов с тремя выходными состояниями, выходное слово передаётся на внешнюю шину. 6.3 Оперативные запоминающие устройства 6.3.1 Типы оперативных запоминающих устройств В зависимости от способа хранения информации оперативные запоминающие устройства (ОЗУ) подразделяются на статические и динамические. В статических ОЗУ (Static RAM — SRAM) запоминающими элементами являются триггеры, сохраняющие своё состояние, пока схема находится под питанием и нет новой записи данных. В динамических ОЗУ (Dynamic RAM — DRAM) данные хранятся в виде зарядов конденсаторов, образуемых элементами МОП-структур. Саморазряд конденсаторов ведёт к разрушению данных, поэтому они должны периодически (каждые несколько миллисекунд) регенерироваться. В то же время плотность упаковки динамических элементов памяти в несколько раз превышает плотность упаковки достижимую в статических RAM. Регенерация данных в статических ЗУ осуществляется с помощью специальных контроллеров. Разработаны также ЗУ с динамическими запоминающими элементами, имеющие внутреннюю встроенную систему регенерации, у которых внешнее поведение относительно управляющих сигналов становится аналогичным поведению статических ЗУ. Такие ЗУ называются квазистатическими. В целом динамические ЗУ характеризуются наибольшей информационной ёмкостью и невысокой стоимостью, поэтому именно они используются как основная память ЭВМ. Статические ОЗУ делятся на асинхронные и тактируемые. В асинхронных ЗУ сигналы управления могут задаваться как импульсами, так и уровнями. Например, сигнал разрешения работы В тактируемых ЗУ некоторые сигналы обязательно должны быть импульсными. Например, сигнал разрешения работы Статические ЗУ в 4…5 раз дороже динамических и приблизительно во столько же раз меньше по информационной ёмкости. Их достоинством является высокое быстродействие. Область применения относительно дорогостоящих статических ОЗУ в системах обработки информации определяется именно их высоким быстродействием. Типичной областью применения статических ОЗУ в ЭВМ являются схемы КЭШ-памяти. Запоминающими элементами статических ОЗУ служат триггеры с цепями установки и сброса. Триггеры можно реализовать по любой схемотехнологии (ТТЛШ, И²Л, n-МОП, КМОП и др.), в соответствии с которой разработаны разнообразные схемы ЗУ с различными параметрами. 6.3.2 Основные параметры ЗУ Важнейшими параметрами ЗУ являются информационная ёмкость и быстродействие. Информационная ёмкость — максимально возможный объём хранимой информации. Выражается в битах или словах (в частности, в байтах). Бит хранится запоминающим элементом (ЗЭ), а слово — запоминающей ячейкой (ЗЯ), т.е. группой ЗЭ, к которой возможно лишь одновременное обращение. Быстродействие (производительность) ЗУ оценивают временами записи, считывания и длительностями циклов записи/чтения. Время записи — интервал после появления сигнала записи и установлением ЗЯ в состояние, задаваемое входным словом. Время считывания — интервал между моментами появления сигнала чтения и слова на выходе ЗУ. Циклы записи и чтения — это время между двумя последовательностями записи или чтения. Длительности циклов могут превышать времена записи и чтения, так как после этих операций может потребоваться время для восстановления начального состояния ЗУ. Кроме основных (эксплуатационных или измеряемых) параметров, ЗУ характеризуются рядом режимных параметров, обеспечение которых необходимо для нормального функционирования ЗУ. Поскольку ЗУ имеют несколько управляющих сигналов, то для них задаются не только длительности, но и взаимное положение во времени. 6.3.3 Внешняя организация и временные диаграммы статических ОЗУ В номенклатуре статических ЗУ представлены микросхемы с одноразрядной и словарной организацией. Внешняя организация статического ЗУ ёмкостью 64 Кбита (8К×8) показана на рисунке 68. Один из возможных наборов сигналов ЗУ.  Рисунок 68 Пример внешней организации статического ЗУ A — адрес. Разрядность n определяется числом ячеек ЗУ, т.е. максимально возможным числом хранимых в ЗУ слов N=2n, а n=log2N. Например, ЗУ с ёмкостью 8К слов имеет 13-разрядные адреса, выражаемые словами A=a12a11a10…a0, а с ёмкостью 64К слов — 16-разрядные адреса: A=a15a14a13…a0. DI и DO — шины входных и выходных данных; m — их разрядность. В рассматриваемом примере DI и DO объединены в общую шину DIO. CS — выбор кристалла разрешает или запрещает работу данной микросхемы. R/W — чтение или запись. R/W=1 — «Чтение», R/W=0 — «Запись». CE — Chip Enable — разрешение по выходу, пассивное состояние которого Таблица 9 Задание режимов работы микросхемы ЗУ

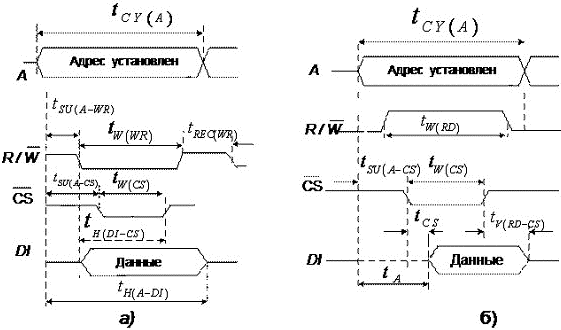

Рисунок 69 Временные диаграммы процессов записи а) и чтения б) в статическом ЗУ Функционирование ЗУ во времени регламентируется временными диаграммами, устанавливаемые изготовителями. В основу кладутся определённые требования. Например, чтобы исключить возможность обращения к другой ячейке, рекомендуется подавать адрес раньше, чем другие сигналы, с опережением на время его декодирования. Адрес должен держаться в течение всего цикла обращения к памяти. Затем следует подать сигналы, определяющие направление передачи данных и, если предполагается запись, то записываемые данные, а также сигнал выборки кристалла. Среди этих сигналов будет и стробирующий, т.е. выделяющий временной интервал непосредственного выполнения действия. Таким сигналом для разных ЗУ может служить как сигнал R/W, так и сигнал Если задана операция чтения, то дополнительно подаётся сигнал разрешения выхода. После подачи указанных выше сигналов ЗУ готовит данные для чтения, что требует определённого времени. По заднему фронту сигнала R, положение которого должно обеспечивать установление правильных данных на выходе ЗУ, данные считываются из ЗУ. Требования к взаимному расположению двух сигналов (например, A и B) задаётся временами предустановки, доступа, удержания и сохранения. Время предустановки сигнала A относительно сигнала B: tSU(A–B) — это интервал между началами обоих сигналов. На рисунке 69 а, б обозначено tSU(A–CS) и tSU(A–WR). Это времена предустановки сигналов CS и WR относительно адреса. Время доступа обозначается символом A (от слова Access) — интервал времени от появления того или иного управляющего сигнала до появления информационного сигнала на выходе. Время доступа относительно адреса tA(A) часто обозначается просто tA. Аналогично этому, время доступа относительно сигнала CS, т.е. tA(CS) обозначают tCS. Время удержания — интервал между началом сигнала A и концом сигнала B tH(A–B). На рисунке 69,б время tH(A–DI) удержания адреса относительно снятия входных данных представляет собой «цикл чтения», а tH(DI–CS) — время подготовки входных данных. Время сохранения tV(A–B) — интервал между окончанием сигнала A и окончанием сигнала B. На рисунке 69,б интервал tV(RD–CS) означает время сохранения данных относительно сигнала «Выбор кристалла» (или сигнала чтения). Этот интервал необходимо обеспечить для уменьшения вероятности появления ошибки при чтении «неустановившейся» информации. Длительность сигнала обозначается tW (индекс от слова Width — ширина). 6.3.4 Микросхемы ОЗУ В последнее время наиболее интенсивно развиваются статические ОЗУ выполненные по технологии КМОП, которые по мере уменьшения топологических норм технологического процесса приобретают всё более высокое быстродействие при сохранении своих традиционных преимуществ. МС К155РУ2 — представляет собой ОЗУ со структурой 2D и с организацией 16×4=64 (Рисунок 70,а). МС изготовлена по технологии ТТЛ. Массив ЭП представляет собой матрицу, состоящую из 16 строк и 4 столбцов. Элементы каждого из столбцов соединены внутренней разрядной линией данных и хранят одноимённые биты всех слов. Ячейка памяти состоит из 4-х триггеров, управляемых общим сигналом. При CS=0 одна из ячеек, соответствующая выставленному адресу, переходит в рабочее состояние, её сигналы поступают на входы элементов И(7…10). При CS=1 на всех выходах дешифратора низкие уровни и, следовательно, все триггеры отключены от входных шин накопителя. При CS=0 и W=0 на выбранную ячейку поступают информационные сигналы с входов D1…D4 и элементом И1 вырабатывается сигнал «Запись». Входная информация со входов D1…D4 записывается в ячейку. При CS=0 и W=1 формируется сигнал «Чтение» и информация из выбранной ячейки читается с выходов Q1…Q4.  Рисунок 70 МС К155РУ2: а) Структурная схема, б) Условное обозначение Микросхемы К176РУ2, К561РУ2 с организацией 256×1 изготовлены по технологии КМОП и представляют собой ЗУ со структурой 3D (Рисунок 71,а).  Рисунок 71 Микросхема К176РУ2: а) Структурная схема; б) Элемент памяти. Структурная схема МС К176РУ2 приведена на рисунке 71,а. Схема содержит два дешифратора: DC столбцов и DC строк. Дешифраторы имеют по 4 входа, на которые подаётся по 4 разряда из общего 8-разрядного адреса, и по 16 выходов. Каждая ячейка памяти находится на пересечении строки и столбца, поэтому два дешифратора обеспечивают обращение к 16×16=256 элементам памяти. Каждый элемент памяти представляет собой статический RS-триггер (рисунок 71,б). Триггер имеет два парафазных входа/выхода. С разрядными шинами РШ0 и РШ1 триггер соединён через ключи VT5 и VT6. По разрядным шинам к триггеру подводится при записи и отводится при считывании информация в парафазной форме представления по РШ1 своим прямым значением, а по РШ0 — инверсным. В режимах «Запись» и «Чтение» при возбуждении строки сигналом выборки Xi=1, снимаемым с дешифратора адреса строк, ключи VT5 и VT6 открываются и подключают триггер к разрядным шинам. При Xi=0 ключи закрыты и триггер отключён (изолирован) шин, а информация в них хранится. При считывании информации ключи подключают элемент памяти к разрядным шинам, они принимают потенциалы выходов триггера и через устройство ввода/вывода передают их на выход микросхемы. РШ охватывают все элементы одного столбца, а переходит в активное состояние только один ЭП, соответствующий выбранной строке. Из него и считывается информация. Среди отечественных серий микросхем хорошо развитыми являются серии К537 технологии КМОП с информационной ёмкостью от 1024×1 (К537РУ1) до 8192×8 (К537РУ17) и К132 технологии n-МОП с информационной ёмкостью от 1024×1 (К132РУ2) до 65536×1 (К132РУ10). Ориентировочные значения основных параметров ОЗУ различных технологий приведены в таблице 10. Таблица 10 Значения основных параметров ОЗУ

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Главная | Контакты | Нашёл ошибку | Прислать материал | Добавить в избранное |

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

может оставаться неизменным и разрешающим на протяжении многих циклов обращения к памяти.

может оставаться неизменным и разрешающим на протяжении многих циклов обращения к памяти. переводит выходы в третье состояние. Работа ЗУ отображается таблицей (таблица 9).

переводит выходы в третье состояние. Работа ЗУ отображается таблицей (таблица 9).